## TeeJam: Sub-Cache-Line Leakages Strike Back

Florian Sieck<sup>1</sup>, Zhiyuan Zhang<sup>2\*</sup>, Sebastian Berndt<sup>1</sup>, Chitchanok Chuengsatiansup<sup>2\*</sup>, Thomas Eisenbarth<sup>1</sup> and Yuval Yarom<sup>3\*</sup>

<sup>1</sup> University of Lübeck, Lübeck, Germany {florian.sieck,s.berndt,thomas.eisenbarth}@uni-luebeck.de <sup>2</sup> The University of Melbourne, Melbourne, Australia zhiyuanz5@student.unimelb.edu.au,c.chuengsatiansup@unimelb.edu.au <sup>3</sup> Ruhr-University Bochum, Bochum, Germany yuval.yarom@rub.de

**Abstract.** The microarchitectural behavior of modern CPUs is mostly hidden from developers and users of computer software. Due to a plethora of attacks exploiting microarchitectural behavior, developers of security-critical software must, e.g., ensure their code is constant-time, which is cumbersome and usually results in slower programs. In practice, small leakages which are deemed not exploitable still remain in the codebase. For example, sub-cache-line leakages have previously been investigated in the CacheBleed and MemJam attacks, which are deemed impractical on modern platforms.

In this work, we revisit and carefully analyze the 4k-aliasing effect and discover that the measurable delay introduced by this microarchitectural effect is higher than found by previous work and described by Intel. By combining the rediscovered effect with a high temporal resolution possible when single-stepping an SGX enclave, we construct a very precise, yet widely applicable attack with sub-cache-line leakage resolution. To demonstrate the significance of our findings, we apply the new attack primitive to break a hardened AES T-Table implementation that features constant cache line access patterns. The attack is up to three orders of magnitude more efficient than previous sub-cache-line attacks on AES in SGX. Furthermore, we improve upon the recent work of Sieck et al. which showed partial exploitability of very faint leakages in a utility function loading base64-encoded RSA keys. With reliable sub-cache-line resolution, we build an end-to-end attack exploiting the faint leakage that can recover 4096-bit keys in minutes on a laptop. Finally, we extend the key recovery algorithm to also work for RSA keys following the standard that uses Carmichael's totient function, while previous attacks were restricted to RSA keys using Euler's totient function.

Keywords: Side-Channels  $\,\cdot\,$  Microarchitectural Attacks  $\,\cdot\,$  Trusted Execution Environments

## 1 Introduction

Performance and functionality of modern processors evolve in short intervals and improvements over previous generations are usually significant. To allow for this rapid development, microarchitectural features like caching and speculative execution have been pushed to their limits, often favoring speed over security. As a result, numerous microarchitectural attacks have been found that exploit non-constant-time behavior caused by caches, branch predictors etc. [OST06, AKS07, LYG<sup>+</sup>15, IAES15]. These attacks were followed by exploits

<sup>\*</sup>Work was partially done while the author was affiliated with the University of Adelaide

of out-of-order and speculative execution [KHF<sup>+</sup>19, LSG<sup>+</sup>18, vSMÖ<sup>+</sup>19, CGG<sup>+</sup>19]. In the meantime, CPU designers have introduced new security features. One prominent example is Trusted Execution Environments (TEEs) such as AMD SEV [KPW16, Adv18] and Intel Software Guard Extensions (SGX) [MAB<sup>+</sup>13, HLP<sup>+</sup>13], which can enhance overall system security if properly used. The introduction of TEEs has led to an increased interest in microarchitectural attacks [XCP15, MIE17, BPS17, BMW<sup>+</sup>18, BMS<sup>+</sup>20, CCX<sup>+</sup>19]. While protecting code and data from direct access, TEEs do not protect against microarchitectural leakages. Instead, the operating system (OS) and/or hypervisor are untrusted and thus allow for a much more powerful adversarial model. The malicious OS scenario has enabled the development of various new attack techniques, with improved attack resolution [MBH<sup>+</sup>20, SBWE21].

The most common strategy to prevent these microarchitectural attacks is by ensuring that protected code is constant-time. That is, the code should contain neither secret-dependent control flows nor data accesses as well as avoiding instructions with data-dependent execution behavior. Implementation of constant-time code, however, is not trivial. As a result, a broad range of tools utilizing various analysis methods has been proposed. A comprehensive overview of constant-time verification tools is provided in a recent study, which showed that correctly using these tools is a challenge to code developers [JFB<sup>+</sup>22]. One possible pitfall is the level of leakage granularity assumed by these tools. While some of these tools assume cache line resolution for attacks [DFK<sup>+</sup>13, WWL<sup>+</sup>17], others such as Microwalk [WMES18, WSPE22] and DATA [WZS<sup>+</sup>18] keep the resolution configurable, leaving the choice to the developer.

Deciding the right level of granularity for a constant-time assumption can be quite tricky. It is widely accepted that cache line granularity can be observed by sophisticated microarchitectural attacks. Thus, security-critical code like cryptographic implementations must ensure constant-time behavior at the cache line level. The case of more fine granular sub-cache-line leakage is less obvious and contested. The quite powerful and generic CacheBleed attack [YGH17] has sub-cache-line resolution, but it has been fixed in the SkyLake processor generation and is no longer applicable. Other sub-cache-line resolution attacks such as MEMJAM [MWES19] are more difficult to perform and apply to fewer scenarios. In MEMJAM, the attacker introduces data-dependent timing behavior in a victim via 4k-aliasing, which is then exploited by measuring the execution time of the victim code. Hence, MEMJAM has much lower temporal resolution and is much noisier than other modern microarchitectural attacks. As timing variations are statistical and small, the application scenarios are limited. In fact, MEMJAM only targeted block cipher implementations. As a result, many cryptographic libraries have decided to ignore subcache-line leakages, as the cost for constant time at the byte level can be high in terms of performance loss.

In this work, we pose two questions on the limits of the spatial and temporal resolution for microarchitectural attacks on trusted execution environments. As of now, there are many attacks on TEEs with a very high temporal resolution down to instruction level [MIE17, CGYZ22, BPS18]. Most of these attacks use the SGX-Step framework [BPS17] to achieve a high temporal resolution. However, the spatial resolution of these attacks so far is limited by a cache line granularity and combinations of single-stepping and cache attacks on the last-level cache exist [SBWE21]. As explained above, a sub-cache-line spatial resolution by a software-based side-channel attack was achieved by MEMJAM and CacheBleed [YGH17, MWES19], but these attacks achieve only a very low temporal resolution. In fact, due to the attacker model, timing in MEMJAM is always observed over complete executions of the victim's program. A natural question is thus whether this tradeoff between temporal and spatial resolution for software-based side-channels when attacking software running in trusted execution environments and whether future attacks will be limited by this bound. In this work, we show how to achieve a spatial resolution far beyond cache line granularity while keeping a temporal resolution on instruction level.

However, achieving this observation granularity does not necessarily imply that the obtained data can be used to construct attacks, as this might, e.g., be hindered by high noise levels rendering the measurements unreliable. Hence, we are also interested in the question whether the observed fine-granular spatial and temporal information can be used to exploit previously unexploitable implementations.

In summary, the research questions to be answered in this work are:

- **RQ1** Can an attack be designed which surpasses current bounds on the combination of spatial and temporal resolution for observations on software running in trusted execution environments? Meaning, can a temporal resolution as fine as single-stepping be combined with a sub-cache-line spatial granularity?

- **RQ2** Can the instruction-wise temporal and sub-cache-line spatial resolution be used to construct new attacks?

To answer RQ1 and RQ2, we revisit and comprehensively analyze the 4k-aliasing effect on modern Intel CPUs. Our careful analysis reveals that, if properly tuned, the delay effect already observed in MEMJAM can be significantly amplified, making the leakage exploitable with much fewer observations. In fact, the observed leakage is greater than reported in MEMJAM, and also exceeds the delays described in the Intel Optimization Reference Manual [Int15] due to the 4k-aliasing effect. We note that the 4k-aliasing effect can lead to significant delays is already explicitly mentioned in the Reference manual. Furthermore, by single-stepping through the victim application, the induced leakage no longer needs to be detected over the full execution, as done in MEMJAM. Instead, our new attack, which we call TEEJAM, can exploit data-dependent leakage for a single instruction, thus significantly improving the level of temporal resolution achieved by the attack. TEEJAM can observe every victim memory read at a granularity of 4 bytes—achieving sub-cache-line resolution—even if the victim is executed inside the context of Intel SGX.

To showcase the power of TEEJAM, we apply this new side-channel to exploit the base64 decoding of RSA private keys in the OpenSSL library. This leakage was previously exploited in Util::Lookup [SBWE21], which managed to degrade the security level of the targeted RSA implementation, making recovery of short RSA keys practical. However, the leakage is not sufficient to completely recover keys of larger sizes, such as 2048- or 4096-bit keys. TEEJAM can observe the exploited key decoding process with up to 16 times higher resolution. Due to the additional leakage, TEEJAM succeeds in reconstructing 4096-bit keys with ease, highlighting the danger of the discovered sub-cache-line leakage and demonstrating for the first time that the 4k-aliasing effect can be used to exploit vulnerable public-key cryptography, not just block ciphers as done by MEMJAM.

In order to implement a full end-to-end attack for reconstructing RSA private keys generated with OpenSSL [CT23], we extend the Heninger-Shacham key reconstruction algorithm [BPS18] with the ability to reconstruct RSA keys not only with Euler totient as defined in the original publication [RSA78], but also with Carmichael totient as defined in the recent RSA standard [MCK<sup>+</sup>16], which is used in many recent implementations such as OpenSSL [CT23][rsa\_sp800\_56b\_gen.c] and sometimes required, e.g., by the FIPS standard for digital signatures [KR13].

Moreover, we further extend the generalization of the Heninger-Shacham algorithm from Util::Lookup [SBWE21]. The reconstruction algorithm from Heninger-Shacham requires side-channel information to be available as an array of bits. Util::Lookup allows the usage of observation partitions instead of an array of bits. We extend the algorithm to support missing observations and unaligned start and end partitions.

Compared to previous work, the generalization of the key reconstruction algorithm presented here necessitates guessing more information in the lower bits of the secret RSA parameters. While the increased uncertainty requires a higher fraction of known bits to be available in the side-channel traces, it enables the reconstruction of keys with Carmichael totient. Our experiments demonstrate that the high-resolution TEEJAM attack yields sufficient information for the reconstruction of these keys.

Additionally, we present the recovery of a 128-bit AES key with a last-round knownciphertext attack using TEEJAM's high resolution. The attacked implementation is protected against cache attackers and cannot be exploited with cache-line resolution. We show that the combined high temporal and spatial resolution provided by TEEJAM enables the reconstruction of the full key while we reduce the number of required encryption traces by three orders of magnitude compared to previous work MEMJAM [MWES19].

#### 1.1 Contribution

In short, our contributions are:

- A thorough analysis and improvement of the MEMJAM 4k-aliasing effect on modern chip architectures and in various scenarios with and without Intel SGX.

- Introduction of the TEEJAM attack, which provides sub-cache-line leakage of memory accesses in SGX, with high temporal resolution.

- An efficient end-to-end attack which recovers 4096-bit RSA keys from the base64 decoding process, whose leakage was believed to be practically unexploitable for larger key sizes. Notably, we show for the first time that 4k-aliasing effect can be used to target public-key cryptography as well.

- An extension of the Heninger-Shacham algorithm to support private keys with Carmichael totient and improvements that enable the reconstruction of keys from observation traces with missing information and unaligned partitions.

- Recovery of an AES secret key with an attack on a T-Table based AES encryption with effective protection against cache line level attackers. We reduce the number of required encryption traces by multiple orders of magnitude compared to previous work.

The source code is available on https://github.com/UzL-ITS/teejam and https://github.com/UzL-ITS/rsa-key-recovery.

#### 1.2 Responsible Disclosure

The vulnerability in OpenSSL's base64 decoding was reported by the author's of Util:: Lookup. We informed the authors of WolfSSL about our findings concerning their cache attack resistant AES T-Table implementation. They acknowledged our findings and added an AES bitsliced implementation.

### 2 Background

The TEEJAM effect is based on microarchitectural details of Intel processors and functions of SGX. This section gives a short overview of the necessary background.

#### 2.1 4K-Aliasing and MemJam

Most Intel processors support out-of-order execution for load and store operations. These operations are tracked by the load and store buffers respectively, while the Memory Order

Buffer (MOB) maintains the order of these operations. According to the Intel memoryordering model, a load operation can be executed earlier than program order as long as it does not execute earlier than a store to the same physical address.

To avoid waiting for address resolution and allow loads to execute early, the processor performs partial matching using the virtual addresses. Recall that during address translation, bits [11:0] of the virtual address are preserved, i.e., they are not changed by the translation. Thus, to test for potential overlap, the processor first matches bits [11:5] of the virtual addresses and if matched, it compares the offsets for overlap. We use the term 4k-aliasing to refer to a situation where two addresses are determined to be potentially overlapping based on this test. The Intel Optimization Reference Manual describes the precondition for 4k-aliasing as follows: two addresses are said to be affected by 4k-aliasing when the "... load and store have the same value for bits 5–11 of their addresses and the accessed byte offsets ... have partial or complete overlap." [Int15][Section 15.8].

When the processor detects 4k-aliasing, it delays the load operation until the physical addresses of both operations have been determined. Conversely, when no 4k-aliasing is detected, the load is not delayed and instead can be executed before the store. It is important to note that the conflicting offsets do not have to be actual conflicts, i.e., they do not have to be on the same physical page. The Intel Optimization Manual specifies a five-cycle penalty for 4k-aliasing.

This delay can be used by an active attacker to obtain sub-cache-line leakage as presented in MEMJAM [MWES19]. The 4k-aliasing leakage, however, is statistical, i.e., several measurements are necessary to reliably observe the delay specified by Intel. The effect is statistical in the sense that both load and stores have to arrive in a short time frame to cause the conflict. Especially, with an attacker trying to induce the delay from a hyper-thread this is not always given. Additionally, the 4k-aliasing effect can be easily disguised by noise and its amplitude depends on the number of conflicting stores in the MOB, which is also not deterministic in a scenario where the conflict is caused by attacking hyper-thread. Consequently, averaging over repeated executions is necessary to obtain reliable results.

#### 2.2 Intel SGX

Intel Software Guard Extensions (SGX) is a Trusted Execution Environment (TEE) targeting at isolating and protecting sensitive workloads in untrusted environments. It consists of several processor instructions and hardware extensions within the processor [HLP<sup>+</sup>13, MAB<sup>+</sup>13]. Intel SGX protects the memory by encrypting all data which leaves the processor. The Memory Management Unit (MMU) transparently takes care of encrypting the data in RAM. Furthermore, software is measured and the result is compared against a pre-computed signed measurement before the enclave is started, also allowing for remote attestation [AGJS13, SJBZ18]. To ensure proper isolation, SGX provides specific instructions for entering (EENTER), resuming (EERESUME), leaving (EEXIT) and asynchronously exiting (AEX) an enclave. When leaving an enclave, SGX stores the current register file in a secure state save area and restores this state when resuming [CD16]. Furthermore, on exit, SGX flushes the L1 data cache and the TLB [CD16, Int23d].

**SGX-Step:** SGX-Step [BPS17] is a framework which uses precise APIC timer interrupts to single-step the execution of an SGX enclave. For that, the APIC timer is reconfigured after every "step" before the enclave is resumed, such that the interrupt triggers when the ERESUME instruction finishes and the first instruction within the enclave is executed. The interrupt routine will only be executed after the current instruction is committed. If the interrupt arrives slightly early, i.e., within the ERESUME, it results in a "zero-step" which can be easily detected by observing page accesses. A more difficult issue are "multi-steps" which execute more than one instruction in the enclave. To avoid this behavior, the timer

interrupt can be tuned to rather cause "zero-steps". Taking timer values before the enclave resumes and directly after the AEX in the interrupt handler allows to measure the time of a single-step [BPS18]. This time is dominated by the duration of ERESUME and AEX, still allows to infer some information about the protected program [BPS18].

**Memory Management:** The management of memory allocations and mapping of memory pages used within SGX remains in control of the host operating system (OS). While the content of the pages is fully under the control of SGX and can only be decrypted by the owning enclave, the host OS allocates the pages and assigns the virtual to physical page mapping. As such, the OS can control meta information of the page table entries like the page access bit or read / write / execute permissions. All pages, however, are allocated within the Enclave Page Cache (EPC), a processor reserved memory region only accessible from within SGX. To ensure that there are no manipulations of the address translation, SGX keeps track of the page mapping in the Enclave Page Cache Map.

#### 2.3 Reconstructing RSA Keys from Partial Information

A common scenario in side-channel attacks is that the side-channel only reveals partial information about the sensitive values. The attacker thus needs to reconstruct the complete sensitive value from partial information. For the case of RSA private keys, Heninger and Shacham [HS09] presented an iterative algorithm that reconstructs RSA keys if some of the bits of the key are flipped. The algorithm makes use of the fact that RSA keys are typically stored in a highly redundant format to allow for faster decoding via the Chinese remainder theorem. Using the relations between the variables stored in the secret key, one can set up a set of *conditions* to relate the single bits of these variables to each other. By starting with few candidates, the algorithm expands these candidates using these conditions and prunes all candidates that are not compatible with their observations (e.g., because too many bits are flipped). This algorithm was extended by Henecka et al. and Paterson et al. [HMM10, PPS12] to allow for more bit flips. Recently, Sieck et al. [SBWE21] extended the algorithm to a different type of observation where the only information gained from the side-channel is whether a continuous block of b bits belongs to a certain set. Sieck et al. showed that this information is sufficient to drop the security level of the observed RSA keys by at least one level, i.e., the attack costs are reduced by a factor of about  $2^{30}$ .

#### 2.4 Attacker Model

In this work, we assume a system level attacker with full control over the OS and firmware, i.e. BIOS and UEFI, of the target machine. Thus, the attacker is capable of reading and manipulating the memory page mapping, isolating cores from the OS scheduler, fixing the processor frequency, disabling processor features like Intel Speed-Step and cache prefetching and starting and stopping enclaves at will as well as configuring interrupts and load custom kernel modules. Thereby, controlled channel attacks, such as SGX-Step [BPS17], which allows single-stepping enclaves, are enabled. Additionally, the attacker has read access to the binary of the targeted program. SGX only protects the program at runtime but does not encrypt the binary itself. The attacker does *not* execute any code within the victim's enclave and cannot modify the enclave binary. In the context of TEEs, as e.g. SGX, these are reasonable assumptions as the goal is to allow users to securely execute software on untrusted machines in, e.g., cloud environments. Similar attacker models are followed by comparable works [BPS18, MBH<sup>+</sup>20, SBWE21]. Additionally, hyper-threading is enabled.

## 3 4K-Aliasing Effect Analysis

To answer our first question about natural limits on the temporal and spatial resolution of attacks, we now take a closer look at known attacks with high spatial resolution. Two of the most prominent such attacks are MEMJAM [MWES19] and CacheBleed [YGH17]. Due to removed cache bank conflicts which only affected older Intel Ivy Bridge and Sandy Bridge CPUs, CacheBleed is not applicable anymore and we thus focus our study on MEMJAM. Our goal is to understand the underlying vulnerability exploited by MEMJAM and related attacks in depth and how to use it to obtain maximum leakage. Taking a closer look at these attacks shows that the 4k-aliasing effect caused by false read-after-write (RaW) dependencies was used in MEMJAM [MWES19] and also in *Microarchitectural Minefields* [SAMJ18]. Both attacks demonstrate that 4k-aliasing delays the load operation issued after a store operation; however, a detailed analysis on the preconditions and effect of 4k-aliasing on the performance penalty is missing.

We investigate the cause and effect of 4k-aliasing in detail. Therefore, we start by verifying Intel's documentation for a conflicting offset, specifically, "... load and store have the same value for bits 5–11 of their addresses and the accessed byte offsets should have partial or complete overlap" [Int15]. Then, we show how the number of store operations executed within a loop on the sibling thread affects the delay caused by 4k-aliasing.

#### 3.1 Measurement Setup

We analyze the effect of 4k-aliasing across hyper-threads with the code listed in Listing 1 and Listing 2. We refer to two sibling logical cores as Thread 0 and Thread 1. Thread 0 measures the execution time of one load operation from a given address, as shown in Listing 1. Thread 1 performs 100 consecutive stores to a given address in an endless loop as shown in Listing 2. For every experiment in this section, we specify the number of repetitions for calculating the average delay. We explore how the operand size, the memory access offset and the number of stores in the loop impact the 4k-aliasing effect. Finally, we present the delay introduced by a 4k-conflict on different processors. Unless otherwise specified, the evaluations in this section are executed on an Intel Core i7-10710U processor with six cores, running Ubuntu 20.04. We configure the processor to run at maximum frequency of 4700 MHz by setting the CPU governor to performance.

| Listing | 1: | Measuring a load op- | - |

|---------|----|----------------------|---|

| eration | on | Thread 0.            |   |

| mfence<br>rdtsc<br>mov r11b,<br>mfence<br>rdtsc | [r10] |  |

|-------------------------------------------------|-------|--|

Listing 2: Performing 100 store operations to the same address on Thread 1.

%rep 100 mov word [%1], cx %endrep

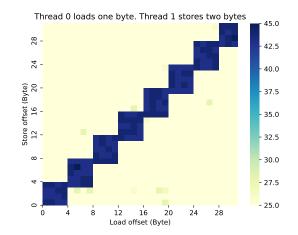

Figure 1: Precondition of 4k-aliasing in terms of address overlaps between conflicting stores and loads. The average time in cycles measured for the memory loads is encoded by color as shown on the right-hand side.

#### 3.2 Bits Overlapping and 4k-Aliasing

In this section, we investigate the overlapping bits of load and store addresses that cause 4k-aliasing. First, we verify 4k-aliasing occurs when bits [11:5] of the load and store addresses are identical, and bits [4:2] are partially or completely overlapping. In the experiment, Thread 0 measures a one-byte load operation from a given address 1,000 times (Listing 1) while Thread 1 infinitely executes 100 two-byte store operations in a loop (Listing 2). We use a two-byte store to show the effect of overlap in bits [4:2]. The load and store addresses are initially pointing to the first byte of two different pages, thus having identical lower 12 bits. We then vary the offset of load and store addresses from byte 0 to byte 31. For each load offset, the average execution time is computed over the 1,000 measurements. The result is shown in Figure 1.

Technically, when storing two bytes to 0x0 on Thread 1 and loading one byte from 0x3 on Thread 0, both operations affect disjunct memory areas. However, as shown in Figure 1, a load operation at offset 0x3 is delayed by a store operation at offset 0x0, which indicates a 4k-aliasing performance penalty. Similarly, a one-byte load at offset 0x0 is delayed by a two-byte store at offset 0x3 although the loaded value is not affected by the stored value. We hypothesize that this effect is caused by the MOB always assuming four-byte aligned load and store operations. For example, a two-byte store to offset 0x3 is treated as if it modifies all data from 0x0 to 0x7 which can also be observed in Figure 1.

Due to the four-byte alignment policy, a load and an earlier store to addresses that share bits [11:5] are considered to be 4k-aliasing if they overlap in bits [4:2]. The results from *Microarchitectural Minefields* [SAMJ18] do not show any alignments above the two bytes stored in their experiment. However, we run our experiments on newer microarchitectures, confirming the leakage features a 4-byte granularity as shown in MEMJAM.

#### 3.3 Number of Conflicting Store Operations

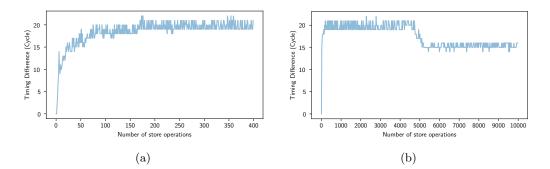

In this section, we demonstrate that 4k-aliasing does not introduce a constant performance penalty, but that the delay is related to the number of conflicting store operations on the sibling logical core. We show that with a proper number of conflicting store operations, 4k-aliasing performance penalty can be increased to 20 cycles under highest processor frequency.

We reuse the code shown in Listing 1 and Listing 2. In this experiment, Thread 1 uninterruptedly executes a certain number of stores to offset 0x0 in an endless loop, while Thread 0 loads an eight-byte value from addresses from the offsets 0x0 and 0x8 alternatingly. The load operation at offset 0x0 will be delayed because of 4k-aliasing. We measure the timing difference between the conflicting and non-conflicting load and change the number of store operations on Thread 1. To reduce measurement noise, we use the average of 500 timed load operations for each address.

First, we investigate the relationship between the performance penalty and the number of stores. Figure 2a shows the increase of the delay when the number of stores is gradually raised from 0 to 400. Around 100 to 200 stores in the loop, the delay is maximal with about 20 cycles difference between the conflicting and non-conflicting load. When further increasing the number of stores in the endless loop, the performance penalty decreases at approximately 4,600 stores as shown in Figure 2b.

As described in Section 2, to re-order a load operation, all older store operations are checked for dependency until a real conflict or 4k-aliasing is detected. In the case that a load operation is 4k-aliasing with a directly preceding store operation, the MOB stops checking the dependency of the load operation with other previous store operations. When the physical addresses of both load and store operations are available and 4k-aliasing turns out to be a false dependency, the MOB starts re-ordering the load operation again and it checks the dependency of the load operation with other store operations. Consequently,

Figure 2: Performance penalty of the 4k-aliasing effect in cycles depending on the number of store operations in the loop of Thread 1. Increasing the number of stores in the loop first raises then reduces the penalty. Figure 2b shows the measurements up to 10,000 stores in the loop of Thread 1, while Figure 2a shows a closer investigation of the range from 0 to 400 stores.

Table 1: 4k-aliasing on different processors. Delay is shown for the base frequency (BF) and the maximum frequency (MF). The latter is measured by setting the Intel pstate driver's governor to "performance".

| Intel Processor | BF<br>(MHz) | Delay BF<br>(Cycles) | MF<br>(MHz) | Delay MF<br>(Cycles) |

|-----------------|-------------|----------------------|-------------|----------------------|

| Core i5-6260U   | 1800        | 36                   | 2900        | 23                   |

| Xeon $E-2286M$  | 2400        | 53                   | 5000        | 26                   |

| Core i5-10210U  | 1600        | 70                   | 4200        | 27                   |

| Core i7-10710U  | 1100        | 78                   | 4700        | 18                   |

fewer store operations in the MOB lead to a smaller delay caused by 4k-aliasing. Thus, the increase of the 4k-aliasing effect shown in Figure 2a can be explained by an increase in the number of address dependency checks. When the MOB is entirely filled with store operations, the effect of 4k-aliasing is maximized. We hypothesize that too many store operations in the loop on the sibling thread cause a slow down in filling the MOB with 4k-aliasing store operations as the front-end is busy with fetching and decoding new store operations. Thus, the number of dependency checks decreases.

### 3.4 MemJam on Different Processors

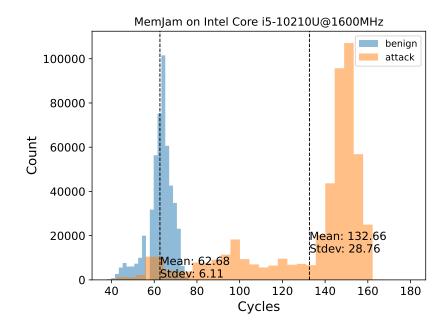

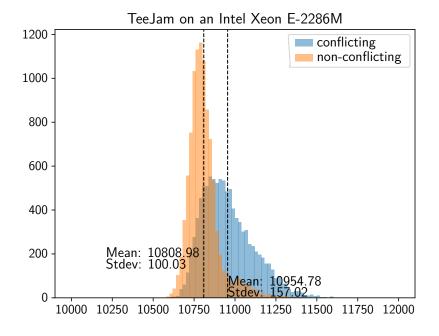

Finally, we present the delay caused by the 4k-conflict on different processors in Table 1 and show a comparison between the timings for loads with and without a 4k-conflict in Figure 3 on an Intel Core i5-10210U at base frequency.

For the results shown in Table 1 and Figure 3 we measure 500,000 times, each conflicting and non-conflicting load. In Table 1 the delay is shown for the processor's base frequency and the processors maximum single-core frequency. On modern Intel processors, the rdtsc instruction measures against a fixed frequency which corresponds to the processor's maximum frequency or the maximum core-clock to bus-clock ratio [Int23e][Vol. 3B, 18.17]. Therefore, a delay measured at lower frequencies appears higher, but in fact remains the same in terms of cycles. Only the temporal measurement resolution is increased compared to the processors running frequency. We show the delay at the maximum frequency as reference and additionally show the base frequency as baseline for a comparison against measurements in Section 4.

Figure 3 shows the distribution of timing measurements for loads with and without

Figure 3: "Conventional" MEMJAM timing measurements with 12 conflicting bits. The measurement is repeated 500,000 times for conflicting (attacked) and non-conflicting (benign) loads.

4k-conflict at the processor's base frequency of 1600 MHz. At this frequency, the average delay is approximately 70 cycles.

## 4 TeeJam: Amplifying 4k-aliasing Leakage with Enclave Interruption

To construct an attack that combines the high spatial resolution of 4k-aliasing leakage with the temporal leakage of single-stepping, we now move the 4k-conflict experiments from Section 3 to the SGX single-stepping context. Many workloads today are executed in trusted execution environments allowing for a stronger attacker model. Our findings show that this combination yields a powerful attack, which we call TEEJAM. TEEJAM inherits the 4-byte intra cache line spatial resolution due to the 4k-aliasing leakage and combines it with the single-instruction temporal resolution of single-stepping, thereby answering our first question positively.

We describe the combination of a 4k-conflict based attack with asynchronous exits from an SGX enclave. As explained in Section 2.1, 4k-aliasing causes the CPU to detect a false read-after-write dependency if a load accesses an aliasing address affected by a preceding store on the same *physical* core, even across hyper-threads. Thus, in a straightforward attack an adversary could determine the addresses of conflicting stores by loading 4kaliasing addresses. As secret-dependent store locations are extremely rare in cryptographic implementations, the effect direction needs to be reversed in order to build a useful attack. In MEMJAM the attacker thread performs conflicting stores to affect secret-dependent loads by the victim on the neighboring hyper-threads.

In fact, MEMJAM provides a sub-cache-line resolution by slowing down loads to specific *offsets* within a specific cache line. All that is left is measuring the caused delay, which is possible but requires millions of observations in a free-running target on the neighboring hyper-threads [MWES19]. MEMJAM thus measured the execution time of

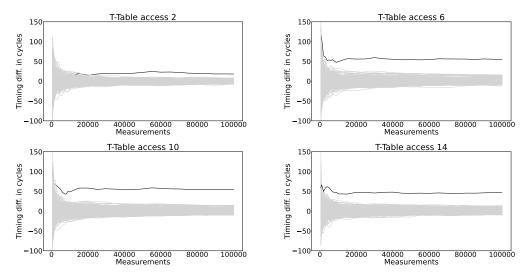

entire encryptions, causing the attack to require millions of observations to recover secret keys from block ciphers. We show that by exploiting the 4k-aliasing leakage in combination with single-stepping the target produces a new attack, achieving both maximal temporal resolution of single-stepping while achieving a 4-byte *intra cache line* resolution, which can thwart implementations that only consider cache-line granularity with ease. We further show that the 4k-aliasing effect is actually amplified by single-stepping into SGX. The delay caused by the false read-after-write dependency is doubled when observed across SGX boundaries, improving the efficiency of the attack. While TEEJAM achieves highest *temporal and spatial* resolution for a microarchitectural attack, we will show that the 4k-aliasing effect remains a statistical one, requiring a low number of repetitions. Yet, we show that single-stepping and the SGX-based leakage amplification allow us to succeed with thousands of observations instead of millions of observations that were necessary in the MEMJAM attack.

In what follows, we describe the measurement setup for determining the amplification of the MEMJAM effect when applied to enclaves and analyze the results on different machines.

#### 4.1 Measurement Setup

We run the basic experiments for evaluating the 4k-aliasing effect on an Intel Xeon E-2286M @2.4 GHz (Coffee Lake) and on an Intel Core i5-10210U @1.6 GHz (Comet Lake). All processors feature Intel SGX. Hyper-threading is enabled and the CPU frequency is fixed to the processor's base frequency. Additionally, to avoid noise in the measurements, we isolate the logical cores used for the measurements from the OS scheduler.

Listing 3: Code for Thread 1: load from #Offset and #Offset + 8.

Listing 4: Code for Thread 2: store to #Offset

| $\pi$ Onset and $\pi$ Onset $\uparrow$ 0.                                                                                          | #Oliset.                                                   |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--|--|--|--|--|

| <pre>void access_for_4k_conflict(     int pos1, int pos2) {</pre>                                                                  | int main() {                                               |  |  |  |  |  |

| <pre>for (int i = 0; i &lt; 100; ++i) {     mem_read(         (uintptr_t) (mem + pos1),         (uintptr_t) (mem + pos2)); }</pre> | <pre>while (1) {     write_conflict(target);     } }</pre> |  |  |  |  |  |

|                                                                                                                                    | •••                                                        |  |  |  |  |  |

|                                                                                                                                    |                                                            |  |  |  |  |  |

| [global mem_read]<br>mem_read:<br>%rep 100                                                                                         | [global write_conflict]<br>write_conflict:                 |  |  |  |  |  |

| mov rax, qword [rdi]                                                                                                               | %rep 100                                                   |  |  |  |  |  |

| mov rax, qword [rsi]                                                                                                               | mov qword [rdi], 100                                       |  |  |  |  |  |

| %endrep                                                                                                                            | %endrep                                                    |  |  |  |  |  |

| ret                                                                                                                                | ret                                                        |  |  |  |  |  |

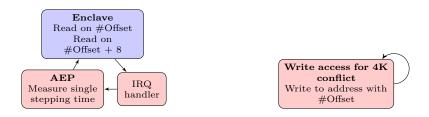

The experimental setup is depicted in Figure 4. The findings of Moghimi et al. in MEMJAM [MWES19] show that the 4k-conflict is highest and best measurable with Readafter-Write (RaW) conflicts, meaning load after store. We transfer MEMJAM RaW conflicts to a TEE scenario. Therefore, load and store operations to pseudo-conflicting offsets are separated onto two threads, as shown in Figure 4a and Figure 4b. Both threads are running on the same physical core but on two different logical cores.

Thread 2, as depicted in Listing 3b, stores continuously and uninterruptedly to a virtual address with page offset #0ffset. On Thread 1, shown in Listing 3a, alternating loads from the offsets #0ffset and #0ffset + 8 are implemented and executed within an SGX enclave. Both addresses are located within the same cache line. We repeat the experiment 10,000 times for each offset. A histogram of the measured single-stepping times for each experiment as well as mean and standard deviation computed over 10,000 experiments are shown in Figure 5. As shown in Figure 4a, the enclave is single-stepped

(a) Measurement flowchart for Thread 1.

(b) Measurement flowchart for Thread 2.

Figure 4: Setup for measuring the effect of 4k-conflict on SGX enclave exits. Thread 1 and Thread 2 are running on sibling logical cores. The enclave accesses alternatingly an address with page offset #Offset and #Offset+8 while it is single-stepped and the time between AEX and ERESUME is measured. Thread 2 continuously stores to an address with page offset #Offset.

with SGX-Step [BPS17] and for every step we measure the single-stepping time, i.e., the time between the call to EERESUME and the return of AEX [BPS18]. The single-steps that belong to the monitored load instructions are filtered by monitoring and manipulating the access bit of the page holding the accessed data.

#### 4.2 Measurement Results

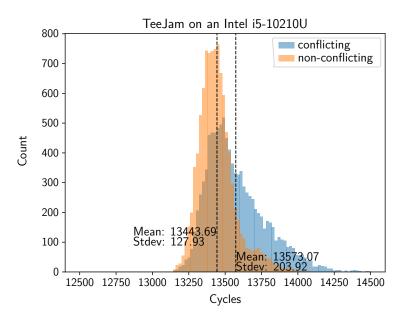

This section presents our measurement results on the Intel Core i5-10210U. Figure 5 shows the results of the TEEJAM effect when single-stepping an enclave with memory loads while simultaneously running a hyper-thread which executes memory stores, as described in Section 4.1.

Figure 5: TEEJAM measurements with 10,000 measurements of the single-stepping time for each the conflicting and non-conflicting load.

When averaging over 10,000 measurements, we obtain results with a distinguishable difference of about 130 cycles in the mean single-stepping time between single-steps with

non-conflicting and conflicting loads. For a comparison, the MEMJAM effect, as shown in Figure 3, causes a delay of 70 cycles on the same processor at its base frequency. Thus, the delay caused by 4k-aliasing is almost twice as big in the SGX setting. The results of the same experiment on the Xeon E-2286M are shown in the Appendix (Figure 16).

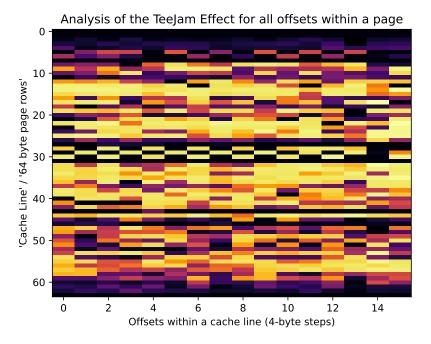

Finally, we repeat the experiment in 4-byte aligned steps over a full memory page to cover all address bits which can be subject to the TEEJAM effect. We proceed in 4-byte chunks since we determined in Section 3.2 that this is the maximum spatial resolution achievable with the 4k-aliasing effect. For mapping the influence of the TEEJAM effect over a whole page, the experiment from Figure 4 is executed with 90,000 instead of 10,000 measurements on the Intel Core i5-10210. For the evaluation, we compute the difference of the means of the conflicting and non-conflicting loads for each 4-byte chunk. The measurement results are shown in the heatmap in Figure 6 that depicts one cache line per row subdivided into 4-byte chunks. We show larger differences in brighter and smaller differences in darker colors. A black field thus depicts a difference of 0.

Of the 1024 executed offsets, the measurements were successful for 852. For the remaining offsets, we were not able to collect proper measurements due to either (i) excessive zero-stepping or (ii) the measurements resulted in two to three times higher single-stepping times accompanied by a very high variance. Since both effects render the corresponding offsets unusable for side-channel attacks, we assigned them a difference of 0.

A close inspection of the heatmap reveals the existence of some cache lines completely unusable for side-channel measurements, especially in the beginning and end, but also isolated throughout the page. Nevertheless, the majority of the cache lines is suitable for TEEJAM.

Figure 6: Mapping the TEEJAM effect over a full memory page. The experiment is repeated in 4-byte aligned steps. The difference between the mean timing measurement of the conflicting and non-conflicting memory accesses are depicted. Dark colors show small differences, while brighter colors depict large differences. We set "unmeasurable" offsets to 0.

#### 4.3 Evaluation

In this section, we evaluate the results from the previous section in more details to conclude that a high temporal and spatial resolution is possible simultaneously, thus answering RQ1 in the positive. The results from the previous section show an increase in the delay by a factor of approximately two between MEMJAM and TEEJAM. This amplification and the large delay of TEEJAM in general allow us to measure 4k-aliasing for memory accesses within enclave execution in a single-stepped fashion, despite the high variance in the single-stepping time. Note, that the original MEMJAM attack measures the delay introduced by a 4k-conflict over the full execution of a program. With TEEJAM, we can measure 4k-conflict on a per-instruction basis and thus drastically increase the timing resolution.

We suspect the reasons for the high variance in the single-stepping time to be attributable to the behavior of the Asynchronous Enclave Exit (AEX) and EERESUME instruction as well as the continuously running hyper-thread that executes the conflicting store instructions. Van Bulck et al. [BPS17] found the ERESUME instruction to be "relatively deterministic". However, in a more recent work, Constable et al. [CVBC<sup>+</sup>23] describe the ERESUME with "... whose execution time itself varies greatly and can take thousands of CPU cycles" and stating that single-stepping is only possible because of a forced microcode assist associated with the first enclave instruction which might take several hundreds of cycles. Additionally, the relatively complex Asynchronous Enclave Exit, which has to cleanup the enclave state and was subject to changes such as flushing the L1 data cache to counteract attacks such as Foreshadow [BMW<sup>+</sup>18], introduces additional noise. Finally, measuring the 4k-conflict requires running application on the hyper-thread co-located with the target enclave. Since both threads share microarchitectural components, the core's pipeline additional noise is introduced and the enclave thread is slightly slowed down. In our experiments, this reflects in a higher APIC timer interrupt time for SGX step compared to an execution without hyper-thread and less reliable single-stepping, meaning more frequent zero-stepping with an appropriately configured APIC timer.

We suspect that the amplification of the MEMJAM effect in SGX is caused by SGX first waiting for all requests in the store and load buffer to be completed before flushing the L1 data cache and TLB. Due to many pseudo-conflicting stores in the store buffer, this process is delayed causing SGX to wait many cycles before flushing the caches and buffers.

As for the applicability of TEEJAM to different offsets, we assume that the difference in the amplitude for most of the working offsets can be explained with measurement noise, i.e. other effects like fetching from last-level cache instead of the second-level cache, which obscures some of the effects. For those offsets, which show excessive zero-stepping or very high single-stepping times and variance, we hypothesize that the 4k-aliasing writes conflict with memory involved in SGX's context switching or the memory translation process during enclave enter and exit [ZMFT22]. A too high variability or the occurrences of such large effects render the timing measurements of these impractical for side-channel attacks. However, the majority of offsets remains fruitful.

RQ1 is answered positively: Single-stepping attacks that achieve a per-instruction temporal resolution can still achieve a sub-cache-line spatial resolution for loads.

#### 4.4 Discussion

In the following we discuss limitations of and potential countermeasures against TEEJAM.

**Intel SGX and Hyper-Threading:** Intel recommends to disable hyper-threading when running secure workloads in Intel SGX [Int23c]. The reasons are attacks like Fore-shadow [BMW<sup>+</sup>18], which can only be fully mitigated by disabling hyper-threading.

Disabling hyper-threading, however, is not desirable in many situations, especially for cloud providers who want to optimize the usage of their resources. Obtaining trusted information about hyper-threading state at runtime is a difficult problem for an enclave [CWC<sup>+</sup>18, OTK<sup>+</sup>18] since the CPUID instruction is not available within the SGX context. However, the hyper-threading state is verified in some attestation scenarios. For Intel's Enhanced Privacy ID (EPID) attestation scheme, the hyper-threading state is reported as part of the attestation report by returning a code which states that further hardening is required if hyper-threading is enabled [Int23c]. In case of the newer Data Center Attestation Primitives (DCAP) attestation scheme, however, the attestation state is only part of the signed attestation data for multi socket systems [Int23a, Section 3.7]. Attestation, however, is only a one-time check of the system configuration and is not necessarily repeated for every initialization of an enclave after keys were exchanged.

Chen et al. [CWC<sup>+</sup>18] propose an instrumentation-based technique to detect hyperthreading and AEX side-channel attackers. However, for the hyper-threading countermeasure they require a running trusted hyper-thread on the co-located core. For shared machines offering trusted execution services to customers on all cores, this essentially reduces to disabling hyper-threading as only half of the logical cores remain available. Furthermore, their approach increases overhead to the target program due to frequent checks for asynchronous enclave exits and trusted validation of a running co-located hyper-thread. Moreover, this countermeasure must be preemptively taken by every enclave, especially in the case of vulnerable library code this poses a problem for practical security. Chen et al. also state that their countermeasure can detect an attacker that applies asynchronous enclave exits, however, to mitigate data-flow leakage this requires many AEX checks which will in turn further increase the overhead.

**Single-Stepping Countermeasures:** Single-stepping SGX enclaves has become a major attack vector. For many years, a plethora of attacks have been enabled by SGX-Step [BPS17]. Thus, it seems only natural that attempts are and were made to reduce the attackers capabilities to mount such attacks. Pridwen [SSL<sup>+</sup>22] is a tool designed to simplify the application of different attack countermeasures to enclave code. However, it only works with enclaves written in WebAssembly and still requires manual application for each enclave. Among others, Pridwen includes the SGX side-channel countermeasure Varys [OTK<sup>+</sup>18]. Varys works in very similar manner to the work of Chen et al. It counteracts AEX based attacks by observing the enclaves state save area and hyper-threading based attacks by colocating a second enclave thread, thus incurring comparable overheads, essentially blocking all logical cores on systems which are used for trusted workloads in shared environments like clouds and requiring manual application to every SGX enclave.

Finally, Intel recently published a revised version of the SGX specification that specifies the AEX-Notify architectural extension [CVBC<sup>+</sup>23, Int22, Int23b]. This extension enables a hardware assisted single-stepping detection and is implemented in microcode and software. However, a target enclave has to enable this feature and register and implement the response to the detected AEX itself by implementing a trusted handler. Thus, while introducing less overhead due to a push mechanism, AEX-Notify still depends on every enclave handling the countermeasures against single-stepping themselves.

**Practical Relevance of TeeJam:** While countermeasures against single-stepping and hyper-threading based attacks against SGX exist, most of these incur significant overhead and all of them require the enclave developer to apply these mechanisms to their enclave themselves. Especially the latter is a problem for vulnerabilities in commonly used cryptographic libraries, which have also been used to construct enclaves. The libraries are general-purpose and thus do not contain such countermeasures. Instead, enclave developers would have to include countermeasures when integrating the library for enclave

usage, resulting in a practical risk that either the countermeasures are not applied at all, applied incorrectly or are incomplete and can be circumvented by sophisticated attackers. Disabling hyper-threading significantly reduces the available computing power and thus increases costs for infrastructure providers which in turn is not desirable. Moreover, a misconfiguration on the server side or a missing or flawed attestation check could lead to the inadvertent activation of hyper-threading. As such, single-stepping and hyper-threading based attacks remain a practical problem, providing further evidence that countermeasures should be applied by default without requiring the developer's intervention.

## 5 Recovering RSA Private Keys with TeeJam

The TEEJAM effect described in Section 4 introduces a novel way to implement an attack achieving high temporal and spatial resolution simultaneously. In this section, we investigate RQ2 and aim to find suitable targets that could not be fully exploited before (due to a lack of spatial or temporal resolution).

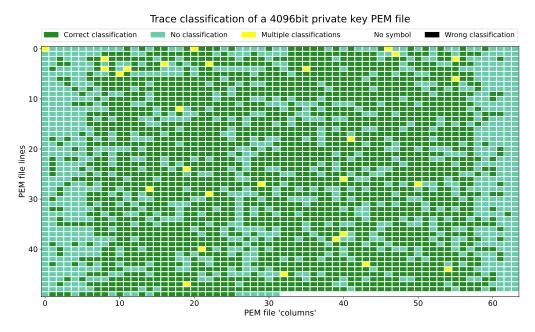

In the scenario studied here, we apply TEEJAM to the decoding of a base64 encoded RSA private key with OpenSSL and demonstrate how the fine granular resolution allows for reconstructing even 4096-bit private keys. This scenario was considered in Util::Lookup but due to a lack of sub-cache-line resolution, it was not possible to reconstruct private keys of length more than 512 bits or 1024 bits without specialized hardware [SBWE21]. Besides significantly extending the range of keys that can be recovered, we also adapt the key reconstruction from Util::Lookup to work with unaligned partitions, missing information, and Carmichael's totient function, allowing us to implement a full end-to-end key recovery attack.

We begin with describing the state of the art RSA key recovery from side-channel leakage obtained from the key file's base64 decoding process, continue with the general idea of how to extract information from base64 decoding in Section 5.3 and then describe the actual attack on the decoding process with TEEJAM in Section 5.4. Finally, we elaborate on the key reconstruction in Section 5.5 and Section 5.6.

#### 5.1 State of the Art RSA Key Recovery from Base64 Decoding

The recovery of RSA private keys from side-channel information gathered during base64 decoding was previously attempted in Util::Lookup [SBWE21]. The attacker in Util:: Lookup exploits that in most cryptographic libraries base64 decoding is implemented with table lookups, translating from base64 symbols to binary. They run a cache attack, specifically a Prime+Probe attack, on a single-stepped enclave. Meaning, they first create eviction sets for the cache lines they want to observe, start the enclave and then, after every step, probe and prime the cache sets. The attack runs in a single trace, meaning in the optimal case it only requires one repetition. More repetitions will not increase the amount of recovered information. However, the obtained information or in other words the maximum leakage is only one bit per access to the lookup table and thus per translated symbol. Due to the uneven distribution of symbols to the cache lines, the real leakage is even below one bit per access. The private key is stored in a heavily redundant way to speed up the decryption operation. Hence, the private key contains five values that are closely related to each other and the attack obtains one bit for each of these five values. The authors of Util::Lookup used this knowledge to employ a combination of the Heninger-Shacham RSA key reconstruction algorithm [HS09] and the lattice algorithm small\_roots in Sagemath based on Coppersmith's method [Cop97] for reconstructing the complete key from this small leakage.

The Heninger-Shacham reconstruction algorithm expects observations on single bits of the key. The information from the Util::Lookup attack, however, delivers information on

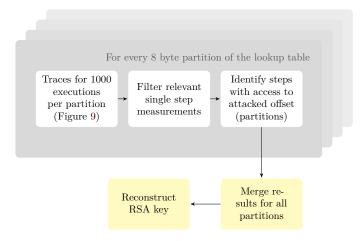

Figure 7: Overview of the attack to reconstruct RSA private keys from execution traces recorded during the key's base64 decoding process.

blocks of size 6 bits. Therefore, the authors generalize the algorithm to work with blocks of variable size. Due to the small leakage, so far only keys with a maximum size of 512 to 1024 bits could be reconstructed with the information from the side-channel attack. The reconstruction of a 512-bit key already requires more than 4,000 CPU hours on commodity hardware and realistic key lengths are thus out of reach for Util::Lookup.

In the next sections, we will show how TEEJAM can be used to significantly increase the amount of leaked information and how this information can then be used to reconstruct even keys with a size of 4096 bits on commodity hardware. Additionally, we will show how RSA keys with Carmichael totient can be reconstructed, which is not possible with the reconstruction algorithm from Util::Lookup.

#### 5.2 Applying TeeJam to Table Lookups

Classical cache attacks provide a maximum spatial resolution of cache-line granularity, i.e., of 64 bytes on modern Intel processors. In the case of base64 decoding where the relevant information in most cases only spreads over two cache lines, the attacker is limited to distinguish between only two sets or partitions of symbols which are translated with the observed steps. Using TEEJAM, the attacker can launch a statistical attack on the victim enclave by provoking 4k-conflicts from a hyper-thread with a granularity of as little as four bytes, potentially splitting a lookup table of 128 bytes into up to 32 partitions. Since TEEJAM is a statistical effect, the decoding has to be observed repeatedly while the attacker provokes conflicts to the same partition. After sufficiently many observations, the same process can be repeated with the next partition. To determine whether the attacked partition was accessed during a table lookup, the attacker computes the average single-stepping time of each observed single-step corresponding to a lookup table access over all observations for which they attacked the same partition. If the average single-stepping time is higher than those of the preceding and following steps, the attacked partition was accessed by the victim.

#### 5.3 Information Retrieval From Base64 Decoding

To reconstruct RSA keys from the information gathered during the decoding of a base64 encoded RSA private key, we proceed in several steps. Figure 7 shows an overview of the complete attack and reconstruction process. First, we collect single-stepping timing traces

| 0x18       ff         |      |    |    |    |     |     |     |     |    |   |    |     |    |     |                                         |   |   |   |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|----|----|-----|-----|-----|-----|----|---|----|-----|----|-----|-----------------------------------------|---|---|---|----|

| 0x10       ff       < |      |    |    |    |     |     |     |     |    | # | ти | N R | LE | , , | 'B                                      |   |   |   |    |

| 0x20       e0       ff         | 0x10 |    |    |    |     |     |     |     |    |   |    | 10  |    |     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |   |   |   |    |

| 0x28       ff ff ff ff 3e       ff f2 ff 3f # + - /       0         0x30       34 35 36 37       38 39 3a 3b # 0 1 2 3 4 5 6 7       1         0x33       3c 3d ff ff ff ff 00 ff ff # 8 9 =       2         0x40       ff 00 01 02       03 04 05 06 # A B C D E F G       3         0x48       07 08 09 0a       0b 0c 0d 0e # H I J K L M N 0       4         0x50       0f 10 11 12       13 14 15 16 # P Q R S T U V W       5         0x68       17 18 19 ff ff ff ff ff ff ff # X Y Z       6         0x60       ff 1a 1b 1c 1d 1e 1f 20 # a b c d e f g       7         0x68       21 22 23 24 25 26 27 28 # h i j k 1 m n o       8         0x70       29 2a 2b 2c 2d 2e 2f 30 # p q r s t u v w       9                                                                                                                                                                                                                                                                                                                                   | 0x18 | ff | ff | ff | ff  | ff  | ff  | ff  | ff |   |    |     |    |     |                                         |   |   |   |    |

| 0x30       34       35       36       37       38       39       3a       3b       #       0       1       2       3       4       5       6       7       1         0x38       3c       3d       ff       ff       ff       00       ff       ff       #       0       1       2       3       4       5       6       7       1         0x38       3c       3d       ff       ff       ff       ff       00       ff       ff       #       8       9       =       2         0x40       ff       00       01       02       03       04       05       06       #       A       B       C       D       E       F       G       3         0x48       07       08       09       0a       0b       0c       0d       0e       #       H       I       J       K       L       M       N       0         0x50       0f       10       11       12       13       14       15       16       #       P       Q       R       S       T       U       W       5         0x50                                                                         | 0x20 | e0 | ff | ff | ff  | ff  | ff  | ff  | ff | # | SF | PAC | Ε  |     |                                         |   |   |   |    |

| 0x38       3c 3d ff ff ff ff 00 0ff ff # 8 9 =       2         0x40       ff 00 01 02 03 04 05 06 # A B C D E F G       3         0x48       07 08 09 0a 0b 0c 0d 0e # H I J K L M N 0       4         0x50       0f 10 11 12 13 14 15 16 # P Q R S T U V W       5         0x58       17 18 19 ff ff ff ff ff ff ff ff # X Y Z       6         0x60       ff 1a 1b 1c 1d 1e 1f 20 # a b c d e f g       7         0x68       21 22 23 24 25 26 27 28 # h i j k 1 m n o       8         0x70       29 2a 2b 2c 2d 2e 2f 30 # p q r s t u v w       9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x28 | ff | ff | ff | Зe  | ff  | f2  | ff  | 3f | # | +  | -   | 1  |     |                                         |   |   |   | 0  |

| 0x40       ff 00       01       02       03       04       05       06       # A B C D E F G       3         0x43       07       08       09       0a       0b       0c       0d       0e       # H I J K L M N O       4         0x50       0f 10       11       12       13       14       15       16       # P Q R S T U V W       5         0x51       17       18       19       ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0x30 | 34 | 35 | 36 | 37  | 38  | 39  | 3a  | Зb | # | 0  | 1   | 2  | 3   | 4                                       | 5 | 6 | 7 | 1  |

| 0x48       07       08       09       0a       0b       0c       0d       0e       # H I J K L M N 0       4         0x50       0f       10       11       12       13       14       15       16       # P Q R S T U V W       5         0x58       17       18       19       ff       ff ff ff ff ff ff ff g X Y Z       6         0x60       ff       1a       1b       1c       1d       1e       1f       20       # a b c d e f g       7         0x68       21       22       32       24       25       26       27       28       # h i j k l m n o       8         0x70       29       2a       2b       2c       2d       2e       2f 30       # p q r s t u v w       9                                                                                                                                                                                                                                                                                                                                                                | 0x38 | Зc | 3d | ff | ff  | ff  | 00  | ff  | ff | # | 8  | 9   | =  |     |                                         |   |   |   | 2  |

| 0x50       0f       10       11       12       13       14       15       16       #       P       Q       R       S       T       U       V       \$         0x58       17       18       19       ff       ff       ff       ff       ff       ff       #       X       Y       Z       6         0x60       ff       1a       1b       1c       1d       1e       1f       20       #       a       b       c       d       e       f       7         0x68       21       22       23       24       25       26       27       28       #       h       i       j <k< td="">       1       m       n       8         0x70       29       2a       2b       2c       2d       2e       2f       30       #       p       q       r       st<u< td="">       u       w       9</u<></k<>                                                                                                                                                                                                                                                          | 0x40 | ff | 00 | 01 | 02  | 03  | 04  | 05  | 06 | # | Α  | В   | С  | D   | Е                                       | F | G |   | 3  |

| 0x58       17       18       19       ff       < | 0x48 | 07 | 08 | 09 | 0a  | 0b  | 0 c | 0 d | 0e | # | Η  | Ι   | J  | Κ   | L                                       | М | Ν | 0 | 4  |

| Ox60         ff         1a         1b         1c         1d         1e         1f         20         # a b         c d e f g         7           Ox68         21         22         23         24         25         26         27         28         # h i j k l m n o         8           Ox70         29         2a         2b         2c         2d         2e         2f         30         # p q r s t u v w         9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0x50 | 0f | 10 | 11 | 12  | 13  | 14  | 15  | 16 | # | Ρ  | Q   | R  | S   | Т                                       | U | V | W | 5  |

| 0x68         21         22         23         24         25         26         27         28         # h i j k l m n o         8           0x70         29         2a         2b         2c         2d         2e         2f         30         # p q r s t u v w         9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x58 | 17 | 18 | 19 | ff  | ff  | ff  | ff  | ff | # | X  | Y   | Ζ  |     |                                         |   |   |   | 6  |

| 0x70 29 2a 2b 2c 2d 2e 2f 30 # p q r s t u v w 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0x60 | ff | 1a | 1b | 1 c | 1 d | 1e  | 1f  | 20 | # | a  | b   | с  | d   | е                                       | f | g |   | 7  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x68 | 21 | 22 | 23 | 24  | 25  | 26  | 27  | 28 | # | h  | i   | j  | k   | 1                                       | m | n | 0 | 8  |

| $0x78$ 31 32 33 ff ff ff ff ff $\frac{4}{5}x$ y z 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x70 | 29 | 2a | 2b | 2c  | 2d  | 2e  | 2f  | 30 | # | р  | q   | r  | s   | t                                       | u | v | W | 9  |

| 0410 01 02 00 11 11 11 11 11 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x78 | 31 | 32 | 33 | ff  | ff  | ff  | ff  | ff | # | x  | у   | z  |     |                                         |   |   |   | 10 |

Figure 8: OpenSSL's base64 decoding lookup table. The boxes indicate the partitions observable with the TEEJAM attack. The partitions are identified by the numbers on their right. The comments list the ASCII representations contained within each partition.

for every partition shown in Figure 8. From these traces, we filter those timings which are related to decoding lookups. The filtered traces for each partition are then analyzed to identify those load operations that accessed the observed partition, meaning the partition attacked with 4k-conflicts. Finally, the results for all partitions are merged and used as input for the RSA key reconstruction algorithm.

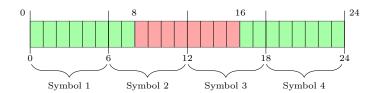

The decoding of base64 in many cryptographic and utility libraries is implemented with lookup tables [SBWE21]. There are minor differences in the implementations, but in general the ASCII code of each base64 symbol is used as the index to an array which holds the associated binary values. As each base64 symbol corresponds to  $\log_2(64) = 6$  bits of information, the base64 decoding algorithm proceeds by concatenating the information from four table lookups into three bytes.

Exemplarily, the lookup table (LUT) used by OpenSSL [CT23] is shown in Figure 8. It has a size of 128 bytes, potentially holding all ASCII characters, and replaces unneeded bytes with 0xff. During the translation of a private key Privacy-enhanced Electronic Mail (PEM) file, OpenSSL parses every base64 symbol twice. First, it collects 64 symbols and translates them to verify their validity, then it iterates over the same chunk of 64 bytes again for the actual decoding.

With a cache attack, the maximum information which can be gathered per lookup is one bit, assuming an equal distribution of symbols per cache line. For the OpenSSL LUT the mutual information is approximately I(B, P) = 0.696 bit for 64-byte alignment of the LUT or I(B, P) = 0.974 bit for 32-byte alignment [SBWE21], where I is the mutual information and the random variables B and P denote the base64 symbol and the partition, respectively. For a cache attack, the partition size is a 64-byte cache line. Util::Lookup shows that this information is enough to reconstruct small keys with a size of 512 bytes or 1024 bytes with sufficient computing resources as well as to decrease the security level of larger keys.

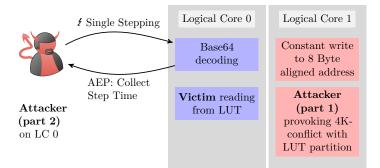

Figure 8 shows the partitioning of the OpenSSL LUT we chose for a sub-cache-line attack with TEEJAM. As shown in Section 3, TEEJAM offers a resolution of up to four bytes. However, we settle, as a tradeoff, for partitions of eight bytes to reduce the amount of necessary observations by 50% and still obtain more than sufficient leakage to reconstruct the decoded keys from the observed side-channel information. Each of the chosen partitions consists of two to eight symbols, depending on the symbol distribution corresponding to the ASCII encoding, as some of the symbols can only occur in certain special positions. More concretely, the symbol '-' does not appear in the base64 standard, but only in some

Figure 9: Attack setup for retrieving traces which yield the accessed lookup table (LUT) partitions. Logical core (LC) 0 and 1 are hyper-threads on the same physical core.

variants. Furthermore, the symbol '=' is only ever used for padding and thus cannot appear in arbitrary positions. Hence, we have two partitions in which 2 symbols are possible, five partitions with 8 symbols, two partitions with 7 symbols, and two partitions with 3 symbols. The entropy is maximized by considering the uniform distribution in each partition, yielding mutual information of

$$I(B,P) = \frac{2 \cdot 2}{64} \cdot \log_2\left(\frac{64}{2}\right) + \frac{5 \cdot 8}{64} \cdot \log_2\left(\frac{64}{8}\right) + \frac{2 \cdot 7}{64} \cdot \log_2\left(\frac{64}{7}\right) + \frac{2 \cdot 3}{64} \cdot \log_2\left(\frac{64}{3}\right) \approx 3.3 \text{ bit}$$

for each correctly detected lookup table access. This is more than half of the total available information of 6 bits and by far enough to reconstruct the decoded private key from the captured leakage, even with imperfect traces that miss some observations. Choosing smaller partitions would require to collect more traces, thus complicating the attack without any real gain for the attacker.

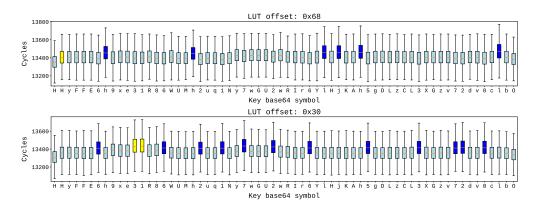

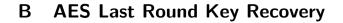

#### 5.4 Lookup Table Trace Recovery