# Browser-Based Microarchitectural Side-Channel Attacks

Sioli O'Connell

A thesis submitted for the degree of DOCTOR OF PHILOSOPHY

The University of Adelaide

Supervised by Yuval Yarom and Damith Ranasinghe

January 2025

# **Contents**

| Co | onten | ts                                                       | iii |

|----|-------|----------------------------------------------------------|-----|

| Li | st of | Figures                                                  | vii |

| Li | st of | Listings                                                 | ix  |

| Li | st of | Tables                                                   | хi  |

| St | atem  | ent of Originality                                       | χv  |

| A  | cknov | wledgements                                              | vii |

| 1  | Intr  | oduction                                                 | 1   |

|    | 1.1   | Analysing Coarse-Grained Side-Channel Leakage            | 3   |

|    | 1.2   | Mounting a High-Capacity Pixel-Stealing Attack           | 5   |

|    | 1.3   | Mounting a Transient-Execution Attack on Modern Browsers | 7   |

|    | 1.4   | Transient-Execution Attacks on Security Type Systems     | 8   |

|    | 1.5   | Summary of Contributions                                 | 9   |

|    | 1.6   |                                                          | 11  |

|    |       | 1.6.1 Other Publications                                 | 12  |

| 2  | Bac   | kground                                                  | 15  |

|    | 2.1   | Microarchitecture                                        | 15  |

|    |       | 2.1.1 Memory Caches                                      | 15  |

|    |       | 2.1.2 Execution                                          | 17  |

|    | 2 2   | Microarchitectural Attacks                               | 18  |

|   |      | 2.2.1   | Cache Timing Attacks                        | 18 |

|---|------|---------|---------------------------------------------|----|

|   |      | 2.2.2   | Transient-Execution Attacks                 | 20 |

|   | 2.3  | Brows   | ers                                         | 21 |

|   |      | 2.3.1   | Same-Site Policy                            | 21 |

|   |      | 2.3.2   | JavaScript                                  | 22 |

|   |      | 2.3.3   | Browser Architecture                        | 23 |

|   |      | 2.3.4   | Uint8Array                                  | 24 |

|   | 2.4  | Brows   | er-Based Attacks                            | 25 |

|   |      | 2.4.1   | Website-Fingerprinting Attacks              | 25 |

|   |      | 2.4.2   | History Sniffing Attacks                    | 26 |

|   |      | 2.4.3   | Pixel-Stealing Attacks                      | 27 |

| 3 | Attr | ihuting | g Microarchitectural Leakage within Systems | 29 |

| J | 3.1  | _       | sis Overview                                | 31 |

|   | 5.1  | 3.1.1   | Measurement Primitives                      | 31 |

|   |      | 3.1.2   | Measurement Collection                      | 33 |

|   |      | 3.1.3   | Experiment Setup                            | 35 |

|   | 3.2  |         | olling Channel Contributions                | 35 |

|   | 3.2  | 3.2.1   | Intracore Contention                        | 36 |

|   |      | 3.2.2   | Interrupt Handling                          | 36 |

|   |      | 3.2.3   | Frequency Scaling                           | 38 |

|   |      | 3.2.4   | Cache                                       | 38 |

|   |      | 3.2.5   | Validating Control                          | 39 |

|   |      | 3.2.6   | Remaining Leakage                           | 40 |

|   | 3.3  |         | ing Channel Contributions                   | 40 |

|   |      | 3.3.1   | Intracore Contention                        | 41 |

|   |      | 3.3.2   | Interrupt Handling                          | 42 |

|   |      | 3.3.3   | Frequency Scaling                           | 43 |

|   |      | 3.3.4   | Cache                                       | 44 |

|   | 3.4  | Measu   | uring Channel Contributions                 | 46 |

|   |      | 3.4.1   | Methodology                                 | 46 |

|   |      | 3.4.2   | Contributions of Channels                   | 47 |

|   | 3.5  | Conclu  | usion                                       | 49 |

|   |      |         |                                             |    |

| 4 | Mou | ınting a | a High-Capacity Pixel-Stealing Attack              | 51 |

|---|-----|----------|----------------------------------------------------|----|

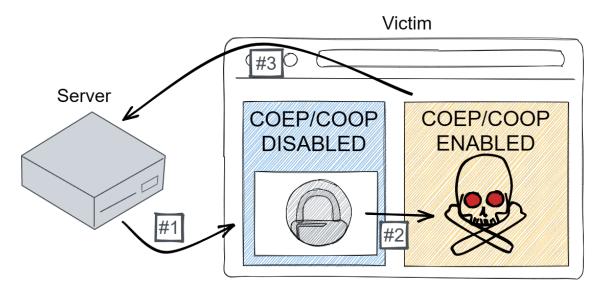

|   | 4.1 | Overco   | oming Cross-Origin Isolation                       | 53 |

|   | 4.2 | Leakin   | g Pixels                                           | 54 |

|   |     | 4.2.1    | The feComponentTransfer Filter                     | 56 |

|   |     | 4.2.2    | Executing feComponentTransfer on the CPU           | 58 |

|   | 4.3 | Recove   | ering Pixels                                       | 61 |

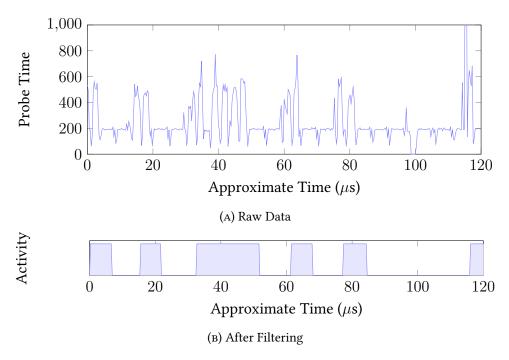

|   |     | 4.3.1    | Detecting Transmitter Communications               | 61 |

|   |     | 4.3.2    | Evaluation                                         | 64 |

|   |     |          | Varying Payload Size                               | 65 |

|   |     |          | Identifying the Target Set                         | 66 |

|   |     |          | System Noise                                       | 67 |

|   |     | 4.3.3    | Comparisons to Existing Works                      | 68 |

|   | 4.4 | From I   | Pixel Stealing to Text Stealing                    | 69 |

|   |     | 4.4.1    | Text Stealing Results                              | 72 |

|   | 4.5 | Histor   | y Sniffing                                         | 72 |

|   |     | 4.5.1    | Straightforward History Sniffing                   | 73 |

|   |     | 4.5.2    | Set Query Optimisation                             | 74 |

|   |     | 4.5.3    | Experiment Description                             | 75 |

|   |     | 4.5.4    | Results                                            | 77 |

|   | 4.6 | Count    | ermeasures                                         | 77 |

|   | 4.7 | Limita   | tions & Future Work                                | 78 |

|   | 4.8 | Conclu   | asions                                             | 79 |

| 5 | Mou | ınting a | a Transient Execution Attack on Modern Browsers    | 83 |

|   | 5.1 | _        | js: Mounting Transient Execution Attacks in Chrome | 84 |

|   |     | 5.1.1    | Website Consolidation                              | 85 |

|   |     | 5.1.2    | Breaking Address Space Isolation                   | 86 |

|   |     | 5.1.3    | Avoiding Deoptimisation                            | 89 |

|   |     | 5.1.4    | Obtaining Deep Speculation                         | 91 |

|   |     | 5.1.5    | End-to-End Attack Performance                      | 94 |

|   | 5.2 | Attack   | Scenarios                                          | 95 |

|   |     | 5.2.1    | Website Identification                             | 95 |

|   |     | 5.2.2    | Recovering Sensitive Information                   | 96 |

| A | Full | Address Calculation                         | 141 |

|---|------|---------------------------------------------|-----|

| 7 | Con  | clusion                                     | 123 |

|   | 6.3  | Conclusion                                  | 120 |

|   | 6.2  | PoC Attack                                  | 118 |

|   | 6.1  | AES Background                              | 117 |

| 6 | Secu |                                             | 115 |

|   | 5.7  | Conclusion                                  | 103 |

|   | 5.6  |                                             | 102 |

|   | 5.5  |                                             | 101 |

|   | 5.4  | Attacking Additional Browsers               | 100 |

|   | 5.3  | Exploiting Malicious Extensions             | 100 |

|   |      | 5.2.5 Exploiting Unintended Content Uploads | 99  |

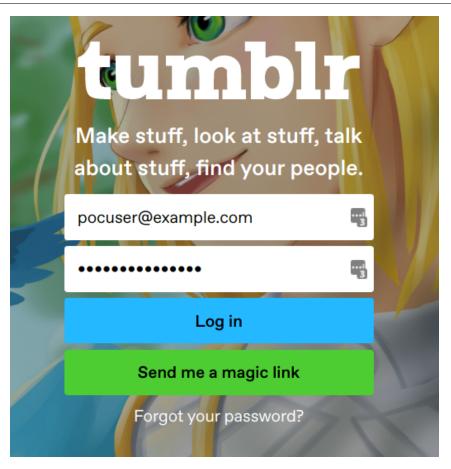

|   |      | 5.2.4 Attacking Tumblr                      | 98  |

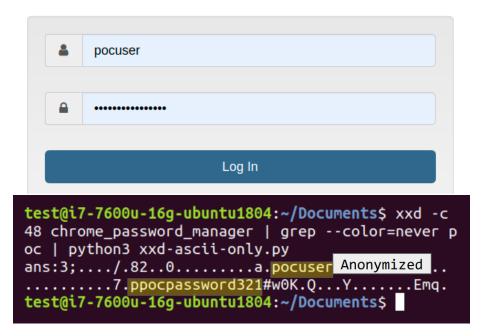

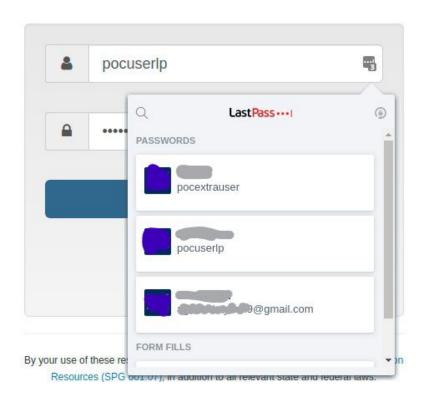

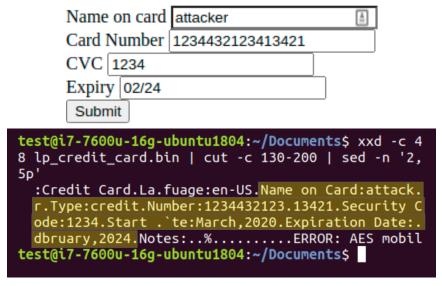

|   |      | 5.2.3 Attacking Credential Managers         | 97  |

# List of Figures

| 2.1  | Uint8Array Memory Layout                | 25 |

|------|-----------------------------------------|----|

| 3.1  | Baseline                                | 34 |

| 3.2  | Reduced Leakage                         | 39 |

| 3.3  | Intracore Leakage                       | 1  |

| 3.4  | Interrupt Leakage                       | 12 |

| 3.5  |                                         | 14 |

| 3.6  |                                         | ŀ5 |

| 4.1  | Overview of a Pixel-Stealing Attack     | 52 |

| 4.2  | Bypassing Cross-Origin Isolation        | 55 |

| 4.3  |                                         | 6  |

| 4.4  |                                         | 53 |

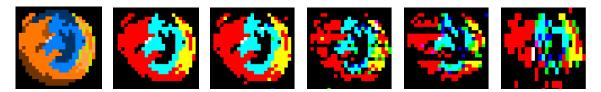

| 4.5  | Recovered Images                        | 55 |

| 4.6  | Packet Size vs. Time & Error Rates 6    | 66 |

| 4.7  | Effect of system noise on leakage       | 57 |

| 4.8  |                                         | 59 |

| 4.9  | Naive Text Stealing Results             | 70 |

| 4.10 | Example Regions                         | 71 |

| 4.11 | Layout of Wikipedia Username            | 72 |

| 4.12 | History Sniffing Memory Access Patterns | 76 |

| 5.1  | Comparing Memory Layout                 | 38 |

| 5.2  | Cacheline Overview                      | 2  |

| 5.3  | Results – Bitbucket – Contents          | )4 |

| 5.4  | Results – Bitbucket – Open Subdomains   | )5 |

### viii

| 5.5  | Results – University – Contact Information    | 106 |

|------|-----------------------------------------------|-----|

| 5.6  | Results – University – Bank Details           | 107 |

| 5.7  | Results – Chrome Password Manager – Passwords | 108 |

| 5.8  | Results – LastPass – Passwords                | 109 |

| 5.9  | Results – Hidden Frame                        | 110 |

| 5.10 | Results – LastPass – Credit Cards             | 110 |

| 5.11 | Results – Tumblr – Password                   | 111 |

| 5.12 | Results – Tumblr – Open Subdomains            | 112 |

| 5.13 | Results – Google Photos                       | 113 |

| 5.14 | Results – Lastpass – Master Password          | 113 |

# **List of Listings**

| 2.1 | SVG Filter Example                                      | 28 |

|-----|---------------------------------------------------------|----|

| 3.1 | Psuedocode for Measurement Primitives                   | 32 |

| 3.2 | Linked-List Element                                     | 33 |

| 4.1 | Malicious filter definition                             | 57 |

| 4.2 | Firefox's feComponentTransfer implementation            | 58 |

| 4.3 | Applying a preamble                                     | 62 |

| 4.4 | History Sniffing CSS Style                              | 73 |

| 5.1 | Pseudocode for Array Accesses                           | 37 |

| 5.2 | Pseudocode for Speculative Type Confusion               | 90 |

| 5.3 | Pseudocode for Finding Objects that Straddle Cachelines | 93 |

| 6.1 | One-Time Pad Example                                    | 16 |

| 6.2 | Protected AES Implementation                            | 21 |

| 6.3 | Pseudocode for AES Attack                               | 22 |

# **List of Tables**

| 3.1 | System Configurations                           | 35  |

|-----|-------------------------------------------------|-----|

| 3.2 | Interrupt Leakage (By device)                   | 43  |

| 3.3 | Correlating Channels and Measurement Primitives | 48  |

| 4.1 | Filter Execution Location                       | 59  |

| 4.2 | Time To Identify a Target Set                   | 67  |

| 4.3 | Comparing Pixel-Stealing Attacks                | 68  |

| 4.4 | Set Query Accuracy Results                      | 81  |

| 5.1 | Spook.js Performance on Various Architectures   | 95  |

| 5.2 | Spook.js Performance on Brave and Edge          | 101 |

### **Abstract**

Web browsers have become a critical component of the modern computing ecosystem. They execute code from websites to enable rich interactions; however, this capability can be exploited by malicious websites to launch attacks directly on user devices. The risk is further amplified by microarchitectural side-channel attacks, which leverage hardware characteristics to leak sensitive data. Although comprehensive theoretical countermeasures exist, they are often impractical for use across entire browsers. As a result, browser vendors have resorted to implementing ad-hoc countermeasures to address these threats.

This issue raises the central question of this thesis: *Are these ad-hoc countermeasures effective in protecting users against microarchitectural side-channel attacks?* To answer this question, the thesis investigates and implements microarchitectural variants of four attack types: website fingerprinting, pixel stealing, memory disclosure, and reduced-round encryption attacks.

The thesis begins by investigating the underlying causes of leakage in three recent microarchitectural website-fingerprinting attacks. The findings reveal that multiple independent sources contribute to the observed leakage, each leaking sufficient information to enable website fingerprinting. These results suggest that effective protection requires comprehensive and multi-faceted countermeasures.

The thesis then introduces two attacks: Pixel Thief and Spook.js, both of which are practical, end-to-end microarchitectural attacks implemented in JavaScript and capable of targeting modern browsers. Pixel Thief is a cache-based pixel-stealing attack that leverages data-dependent memory access patterns in Scalable Vector Graphics filters to recover portions of rendered webpages. Spook.js is a memory disclosure attack that exploits transient type confusion to access arbitrary process memory. Together, these attacks demonstrate that previous mitigation efforts against microarchitectural threats are insufficient.

Finally, the thesis presents a proof-of-concept (PoC) attack against *controlled leakage* in security type systems through a reduced-round encryption attack on the Advanced Encryption Standard (AES). Security type systems enable developers to annotate secret values, allowing the compiler to automatically enforce protections against leakage. These systems often assume sequential execution, however modern processors exhibit out-of-order execution. The PoC attack exploits this mismatch in execution semantics to leak secret values by triggering controlled leakage earlier than the developer intended.

While this thesis shows that ad-hoc countermeasures have been insufficient, it does not claim they are ineffective. The attacks presented here have had reduced impact, required more sophisticated implementation techniques, and required stronger assumptions of adversarial capabilities demonstrating the efficacy of these countermeasures. Furthermore, this work has also informed browser vendors and website operators in the development of new countermeasures that further reduce the threat posed by microarchitectural attacks.

# **Statement of Originality**

I certify that this work contains no material which has been accepted for the award of any other degree or diploma in my name, in any university or other tertiary institution and, to the best of my knowledge and belief, contains no material previously published or written by another person, except where due reference has been made in the text. In addition, I certify that no part of this work will, in the future, be used in a submission in my name, for any other degree or diploma in any university or other tertiary institution without the prior approval of the University of Adelaide and where applicable, any partner institution responsible for the joint award of this degree. The author acknowledges that copyright of published works contained within the thesis resides with the copyright holder(s) of those works.

I give permission for the digital version of my thesis to be made available on the web, via the University's digital research repository, the Library Search and also through web search engines, unless permission has been granted by the University to restrict access for a period of time.

I acknowledge the support I have received for my research through the provision of an Australian Government Research Training Program Scholarship.

# Acknowledgements

I dedicate this thesis to my family and friends, both academic and personal. I genuinely appreciate each and every one of you. Thank you for joining me on this long, difficult, but rewarding journey. Without you, none of this would have been possible.

- Cheers, Sioli

I would like to further thank the following people:

My supervisors Yuval and Damith (and unofficial supervisor Daniel) My co-authors My friends at UofA, UMich and Georgia Tech Finally, my parents Shane and Margaret

# Chapter 1

## Introduction

Over the past thirty years, the Internet has become an integral part of modern life, revolutionising communication by connecting billions of people to each other and to the services they use daily.

The primary gateway to the Internet is the browser, software that connects to and renders websites. Given their central role in connecting users to online services, browsers have become a critical component of the modern computing ecosystem. People rely on them to access everything from routine content to highly sensitive information. As a result, browsers accumulate vast amounts of sensitive data, making them attractive targets for adversaries.

Malicious websites attack browsers by exploiting how browsers, by default, automatically execute code embedded within webpages. This code, typically written in JavaScript, is designed to enable rich, interactive user experiences. However, the same capabilities can be misused by adversaries to launch attacks from within the browser.

Fortunately, browser vendors are aware of these threats, and modern browsers are designed to isolate websites from one another and from the rest of the system. A key component responsible for maintaining this isolation is the JavaScript engine, which executes JavaScript code within the browser. The JavaScript engine enforces several security-critical invariants, such as bounds and type checking, and enables the browser to mediate access to external resources, including the file system, network, and other websites.

The rest of the browser security model is built upon this foundation. If the JavaScript engine fails to maintain its security guarantees, a malicious website may be able to launch attacks against the broader system. This thesis investigates attacks where the JavaScript

engine fails to maintain its security guarantees because the hardware itself failed to maintain its security guarantees.

These attacks exploit optimisations in modern processors that enhance performance by adapting to patterns observed in past program behaviour. These optimisations create a flow of information: from program behaviour to the processor's internal state, and subsequently to the execution time of future operations. Microarchitectural attacks reverse this flow by measuring a program execution time, which reveals constraints on the processor's internal state and, in turn, on the possible past behaviours of a victim program. With enough constraints, an adversary can infer sensitive information processed by the victim.

This thesis focuses on two types of microarchitectural attacks: cache timing attacks and transient execution attacks. The first cache timing attack on browsers was demonstrated by Oren et al. (2015), who adapted an earlier technique for recovering memory access patterns in victim programs (Osvik et al., 2006; Liu et al., 2015) to the browser context. They used this capability to detect network and mouse activity from other websites and other programs running on the system.

The first transient execution attack was published by Kocher et al. (2019). They demonstrated several techniques for manipulating branch prediction in modern processors and showed how this ability could be used to recover sensitive information in various scenarios. One such scenario involved bypassing a bounds check in the JavaScript engine to trigger an out-of-bounds memory access.

These discoveries posed serious challenges for browser vendors, as the security of browser isolation mechanisms assumed the hardware could maintain its security guarantees. Both cache timing and transient execution attacks revealed that these guarantees are not maintained in practice. In, response, browser vendors implemented countermeasures to mitigate the threat of these attacks, including cross-origin isolation (MDN Contributors, 2024b,a) and site isolation (Reis et al., 2019).

Cross-origin isolation limits a website's ability to simultaneously access high-resolution timers and embed third-party content, effectively forcing malicious websites to choose between embedding sensitive third-party content *or* executing cache attacks to recover that content. Site isolation places each website in a separate process to mitigate the threat of transient execution attacks. While transient execution attacks can still access arbitrary process memory, the accesses remain confined to the isolated process.

However, state-of-the-art attack techniques have progressed since the deployment of these countermeasures, prompting the central question of this thesis:

Are cross-origin isolation and site isolation effective techniques to prevent state-of-theart microarchitectural attacks on browsers?

This thesis addresses that question by presenting several novel and practical attacks that bypass these countermeasures to recover sensitive information from modern browsers. The remainder of this chapter provides further introduction to each chapter of the thesis, summarises its key contributions, and outlines its structure.

### 1.1 Analysing Coarse-Grained Side-Channel Leakage

A key challenge in mounting microarchitectural side channels is that they depend on the precise behaviour of the microarchitecture, a behaviour that is rarely documented. Therefore, researchers must rely on experimentation to gather data and construct theoretical models that align with the observed behaviour. The goal is that these models are accurate enough to allow us to design effective countermeasures by accurately predicting the behaviour of the microarchitecture under a variety of conditions.

This approach has proven remarkably effective when applied to individual microarchitectural components, with successful attacks targeting memory caches Liu et al. (2015); Osvik et al. (2006); Percival (2005); Yan et al. (2019); Yarom and Falkner (2014), branch predictors Evtyushkin et al. (2016); Aciiçmez et al. (2007, 2006); Evtyushkin et al. (2018); Zhang et al. (2020), translation lookaside buffers Gras et al. (2018); Koschel et al. (2020); van Schaik et al. (2018), shared buses Paccagnella et al. (2021); Wan et al. (2022), execution units Aciiçmez and Seifert (2007); Bhattacharyya et al. (2019); Aldaya et al. (2019), and GPUs Wei et al. (2020); Naghibijouybari et al. (2018); Taneja et al. (2023); Cronin et al. (2021); Owens and Wang (2011), However, this methodology becomes less effective when analysing the behaviour of the system as a whole.

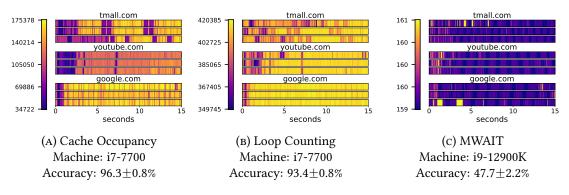

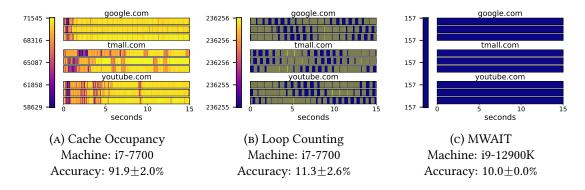

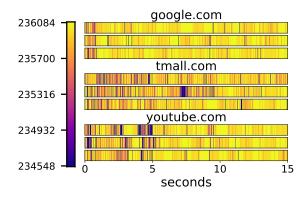

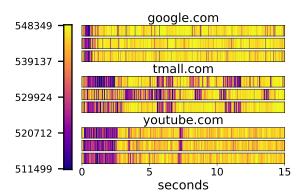

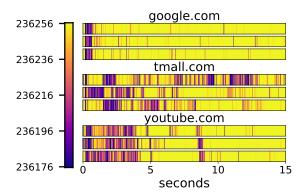

Beyond the inherent complexity of modelling an entire system, accurately attributing observed leakage to specific microarchitectural effects remains a major challenge. This challenge is evident in three recent microarchitectural website-fingerprinting attacks: cache occupancy (Shusterman et al., 2019), loop counting (Cook et al., 2022), and

mwait (Zhang et al., 2023). These attacks identify websites based on site-specific patterns in overall system performance. While their success demonstrates that the system leaks information, pinpointing the exact source of the leakage has been a significant challenge.

In particular, disagreement exists over the source of leakage observed in the cache occupancy attack. Shusterman et al. (2019) attribute the leakage to cache contention, while Cook et al. (2022) suggest interrupts cause the leakage. Which explanation, if any, is correct?

Gülmezoglu (2021) proposes a method for attributing leakage to specific browser behaviours. This approach involves instrumenting the browser to log its behaviour and correlating these logs with microarchitectural activity using hardware performance counters. A machine learning model is then trained to perform website fingerprinting, and explainable AI techniques are used to determine which browser behaviours most influence the model predictions. While this method effectively links leakage to browser-level activity, it does not clarify how information flows through specific microarchitectural channels – a critical detail for designing robust and effective countermeasures.

Cook et al. (2022) take a different approach by controlling various microarchitectural channels to manage leakage within the system. They conduct experiments across multiple system configurations to determine which microarchitectural channels contribute to the observed leakage. While this method helps identify contributing channels, limited control leaves uncertainty about whether the detected leakage stems from controlled channels or from uncontrolled leakage elsewhere.

**Contributions.** Chapter 3 introduces a methodology that addresses these gaps and resolves the conflicting explanations for leakage in the cache occupancy attack.

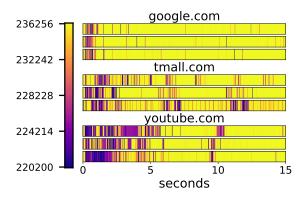

The chapter begins by identifying four microarchitectural channels commonly discussed in the literature: contention for on-core resources, cache contention, interrupts, and frequency scaling. It then demonstrates methods to control each of these channels, resulting in the complete elimination of leakage for the loop counting and mwait primitives, and a significant reduction of leakage for the cache occupancy primitive. These results indicate that the four channels comprehensively explain leakage in the loop counting and mwait cases, while additional uncontrolled channels contribute to leakage in the cache occupancy case. The chapter further investigates these uncontrolled channels through experiments suggesting that the remaining leakage originates off-core, likely

within components of the memory hierarchy (Paccagnella et al., 2021; Dai et al., 2022; Wan et al., 2022; Pessl et al., 2016; van der Veen and Gras, 2023).

With comprehensive control established for the loop counting primitive, the chapter proceeds to identify which of the four channels contribute to leakage. It demonstrates that each channel independently provides enough information to mount a website finger-printing attack, indicating that models and countermeasures focusing on a single channel are incomplete.

To present a more complete picture of leakage, the chapter concludes by quantifying the relative contribution of each channel to the total observed leakage. This quantification is achieved by selecting hardware performance counters that correlate strongly with leakage through specific channels and calculating their correlation with observations from each primitive. The results reveal that the primary contributors to leakage are cache contention for the cache occupancy primitive, frequency scaling for loop counting, and interrupts for mwait, thereby resolving the conflicting explanations for leakage in the cache occupancy attack.

### 1.2 Mounting a High-Capacity Pixel-Stealing Attack

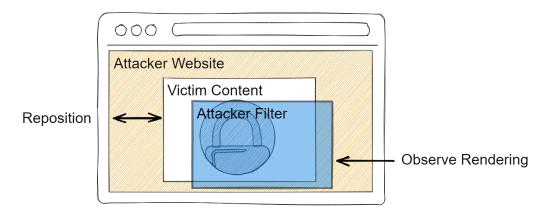

Webpages often include content from multiple sources – the main webpage itself, links highlighted based on the user browsing history, third-party advertisements, social media widgets, and more. Browsers are responsible for rendering all this content as a seamless, cohesive page without leaking sensitive information between the different sources.

One of the key mechanisms browsers use to achieve this is the same-origin policy, which restricts code from one website from accessing content belonging to another website, even if both are embedded within the same webpage. Beyond controlling direct access, browsers also control indirect access including controlling whether code can access the composited output that is displayed to the screen.

Unfortunately, pixel-stealing attacks bypass this control to reveal sensitive information displayed on webpages. Several studies have demonstrated how to reveal the colour of selected pixels by measuring subtle differences in webpage rendering times (Stone, 2013; Kotcher et al., 2013; Andrysco et al., 2015; Kohlbrenner and Shacham, 2017; Wang et al., 2023; Taneja et al., 2023). By repeating this process with different pixels, an adversary can reconstruct arbitrary portions of the webpage.

A fundamental limitation of these attacks is their dependence on measuring the time taken to render the webpage, which restricts the information extraction rate to the browser rendering frequency – typically 60 times per second. Furthermore, browser vendors have actively worked to eliminate these timing differences to mitigate previously published attacks. Although recent studies have shown that CPU and GPU frequency scaling can be exploited to conduct pixel-stealing attacks, these methods result in even lower leakage rates (Wang et al., 2023; Taneja et al., 2023).

Beyond the limitations on the rate of information extraction, browser vendors have widely deployed cross-origin isolation to mitigate a broad range of side-channel attacks. Cross-origin isolation creates a mutually exclusive condition where a website must choose between embedding content from other sources *or* accessing high-resolution timers. As a result, a malicious website cannot simultaneously embed sensitive content *and* use high-resolution timers to mount an attack to recover that content.

**Contributions.** Chapter 4 addresses the question: *Are high-capacity pixel-stealing attacks on modern browsers feasible?* It presents Pixel Thief, a cache-based pixel-stealing attack that bypasses the rate limit imposed by the browser rendering frequency.

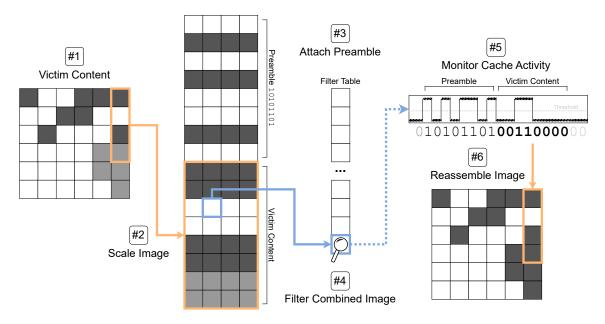

Pixel Thief achieves this by observing data-dependent memory accesses within the feComponentTransfer filter. This filter is applied to sensitive content, an action allowed because the side effects of applying filters are assumed to be unobservable. The filter uses the colour of each pixel in the sensitive content to access a table of colours. The output of the filter is ignored, but its memory accesses are observed using the Prime+Probe technique. Each observed memory access reveals the colour of the pixel used to perform the access. Since the filter performs an access for each pixel, the colour of several pixels can be leaked during a single invocation of the filter. This decouples the leakage rate of Pixel Thief from the browser rendering frequency and overcomes the limitations that constrained previous attacks.

To measure filter memory accesses with Prime+Probe, the chapter introduces a generic technique to bypass cross-origin isolation. This technique splits the attack across two webpages: the first embeds sensitive content, while the second uses high-resolution timers to measure leakage from the first webpage.

The chapter concludes by presenting two end-to-end attacks to demonstrate the effectiveness of Pixel Thief's approach. The first adapts a method from Stone (2013) to modern fonts to increase leakage rates by exploiting redundant information in text,

then uses this method to reveal the victim's Wikipedia identity. The second abuses link highlighting to construct an oracle that reveals whether the user previously visited a specific URL, then queries the oracle with a large number of URLs to partially reconstruct the victim's browsing history.

### 1.3 Mounting a Transient-Execution Attack on Modern Browsers

The discovery of transient execution attacks sent shockwaves through the industry. Browsers were particularly vulnerable, as they used software-based isolation techniques to separate content rendered onto the same webpage. Unfortunately, transient execution attacks bypass many software-based techniques by enabling adversaries to transiently execute code before critical security requirements are verified.

In response, Google deployed site isolation for the Chrome browser (Reis et al., 2019). This countermeasure separates content from different origins into separate processes. While it does not prevent transient execution attacks from accessing arbitrary memory within a process, it mitigates the threat of transient execution attacks by leveraging process isolation guarantees provided by the hardware.

Beyond hardware-based isolation, Chrome employs pointer compression, representing each pointer as a 32-bit offset from a base address. This reduction in pointer size saves memory but also restricts the memory accessible to each pointer. Chrome leverages this limitation, combined with a specialised allocator, to partition the address space and confine out-of-bounds memory accesses.

**Contributions.** Chapter 5 addresses the question: *Are practical transient-execution attacks on modern browsers feasible?* The chapter presents Spook.js, a transient-execution attack capable of extracting sensitive information despite the countermeasures deployed by Chrome.

The chapter begins by highlighting a gap between policies used by the browser to define the security boundaries between websites. Typically, the same-origin policy defines the boundary between two websites and is often the boundary developers consider when designing websites. Site isolation, however, uses the same-site policy to define the boundary between two websites. This gap creates a scenario where websites considered

distinct by developers are combined into the same process undermining site isolations security benefits.

To bypass Chrome's address space partitioning and access memory from other websites, the chapter demonstrates a type-confusion attack which tricks Chrome into accessing a malicious object as a typed array. Since typed arrays can be shared between webpages, Chrome allocates them outside of any specific partition and uses a full-sized pointer to refer to the contents of the typed array. Spook.js crafts a malicious object that takes control over this pointer to access memory anywhere in the process.

To demonstrate the practicality of Spook.js, the chapter presents several attack scenarios grouped by adversarial capabilities. First, scenarios where the adversary controls a webpage (e.g., a user homepage) and recovers sensitive content displayed on the same site. Next, scenarios where the adversary uploads content to a cloud service and retrieves other user data stored on that service. Finally, scenarios where the adversary installs a malicious extension on the victim's browser and extract data stored in other extensions.

The chapter concludes by revealing that other browsers, particularly Chrome-based browsers such as Chromium, Brave, and Edge, are also vulnerable to Spook.js with minimal adaptation.

# 1.4 Transient-Execution Attacks on Security Type Systems

Cryptographic constant-time programming is a widely used technique to mitigate sidechannel attacks. It involves transforming a program so that its observable behaviour remains consistent regardless of any secret data. Typically, this transformation is performed manually, which can be both time-consuming and error-prone

One way to automate this process is through the use of a security type system, a programming language feature that enables developers to annotate variables in their programs with **secret** or **public** labels. Tools such as the FaCT compiler (Cauligi et al., 2019) then use type checking and information-flow analysis to ensure data stored within secret variables can never leak into public variables.

While this approach is effective, it can be overly restrictive. It prohibits any side effect from depending on secret variables, even when such dependencies are intentional and do not pose a security risk. Consider, for example, an encrypted messaging application. Encryption takes a message and a key as inputs, both of which are stored in secret variables to protect their integrity. The output is an encrypted message and is safe to reveal. It is stored in a public variable so that it can be sent over the network. However, because the encrypted message is derived from the secret key and message, the compiler will reject the program.

A common solution to this problem is to introduce a **declassify** operation. This operation serves as an annotation inserted by the developer to assert that a value obtained from a secret variable is safe to reveal. In the example above, the developer would insert a declassify operation after encrypting the message so that it can be sent over the network.

**Contributions.** Chapter 6 addresses the question: Can values in secret variables unintentionally leak even when declassification is applied correctly?.

The chapter answers the question in the negative, demonstrating a PoC attack on several implementations of AES, including industry-standard versions and those protected by the FaCT compiler. The attack exploits branch prediction and out-of-order execution in modern processors to coerce the processor into declassifying an output before encryption is correctly applied. Since the output is declassified, the compiler allows it to be revealed.

The chapter provides details for the PoC attack while the accompanying paper (Shivakumar et al., 2023) provides the full theoretical analysis, methods to recover the key from recovered ciphertexts, and proposed countermeasures to mitigate the issue.

### 1.5 Summary of Contributions

In summary, the contributions of this thesis are as follows:

#### **Analysing Coarse-Grained Website-Fingerprinting**

- Describes how to control microarchitectural channels to eliminate leakage (Section 3.2).

- Establishes that all identified channels contribute to website fingerprinting attacks (Section 3.3).

• Quantifies leakage through each channel across multiple website finger printing attacks (Section 3.4).

#### Mounting a High-Capacity Pixel-Stealing Attack

- Develops a simple method to bypass cross-origin isolation, enabling the use of high-resolution timers alongside embedded third-party content (Section 4.1).

- Introduces Pixel Thief, a cache-based pixel-stealing attack that exploits content-dependent memory access patterns in the feComponentTransfer SVG filter to achieve data extraction rates exceeding the browser rendering frequency (Sections 4.2 and 4.3).

- Adapts techniques for rapid text recovery using pixel stealing (Section 4.4).

- Demonstrates a fast history-sniffing attack leveraging cache-based pixel stealing (Section 4.5).

#### Mounting a Transient-Execution Attack on Modern Browsers

- Introduces Spook.js, a transient memory-disclosure attack capable of reading arbitrary memory within rendering processes (Section 5.1).

- Examines the limitations of site isolation and identifies conditions under which multiple websites are consolidated into the same process (Section 5.2).

- Investigates the security implications of Spook.js on Chrome extensions (Section 5.3).

- Confirms that other Chromium-based browsers, including Microsoft Edge and Brave, are also vulnerable to Spook.js (Section 5.4).

#### **Transient-Execution Attacks on Security Type Systems**

• Demonstrates PoC attacks on protected implementations of AES (Chapter 6).

#### **Open Source Code Releases**

As part of this thesis, the following open-source code releases have been made:

- https://github.com/0xADE1A1DE/PixelThief

- https://github.com/spookjs/spookjs-poc

#### 1.6 Structure of Thesis

Chapter 2 – Background – provides the essential background on microarchitectural attacks. It offers a general overview of the behaviour of key microarchitectural components, explains how measurement primitives exploit this behaviour to extract information, reviews the history of attacks based on these primitives, and discusses various browser features relevant to each attack.

Chapter 3 – Analysing Coarse-Grained Side-Channel Leakage – presents and evaluates a methodology for investigating leakage in coarse-grained side channels.

This chapter has not yet been published. In this work, I developed the approach to control channels and eliminate leakage, designed the method to establish leakage through each channel, and supervised experiments conducted by a co-author.

Chapter 4 – Mounting a High-Capacity PIxel Stealing Attack on Modern Browsers – presents and evaluates a practical, high-capacity attack that recovers portions of rendered webpages.

This chapter is based on the following publication: Sioli O'Connell, Lishay Aben Sour, Ron Magen, Daniel Genkin, Yossi Oren, Hovav Shacham, and Yuval Yarom – "Pixel Thief: Exploiting SVG Filter Leakage in Firefox and Chrome", USENIX Security 2024.

In this work, I developed the architecture to bypass cross-origin isolation, identified data-dependent behaviours in SVG filters, and designed and implemented Pixel Thief to exploit these behaviours. I also designed the text-stealing attack, supervised its implementation by a co-author, and designed and implemented the history-sniffing attack.

Chapter 5 – Mounting a Transient Execution Attack on Modern Browsers – demonstrates the first practical transient execution attack on browsers and evaluates it under several attack scenarios.

This chapter is based on the following publication: Ayush Agarwal, Sioli O'Connell, Jason Kim, Shaked Yehezkel, Daniel Genkin, Eyal Ronen, and Yuval Yarom – "Spook.js: Attacking Chrome Strict Site Isolation via Speculative Execution", IEEE SP 2022.

In this work, I designed and implemented the Spook.js attack, including using type confusion to break out of Chrome's partitioned address spaces, identifying suitable malicious objects, preventing deoptimisation through nested speculation, widening the speculation window via last-level cache evictions, and porting Spook.js to other Chromium-based browsers.

Chapter 6 – Declassification and Transient Execution – explores the interaction between security type systems and transient execution.

This chapter has been published as Basavesh Ammanaghatta Shivakumar, Jack Barnes, Gilles Barthe, Sunjay Cauligi, Chitchanok Chuengsatiansup, Daniel Genkin, Sioli O'Connell, Peter Schwabe, Rui Qi Sim, and Yuval Yarom – "Spectre Declassified: Reading from the Right Place at the Wrong Time", IEEE SP 2023.

In this work, I developed the PoC attack used to extract partial ciphertexts from OpenSSL and FaCT implementations of AES.

Chapter 7 – Conclusions – summarises the results, discusses their implications for browser security, and outlines directions for future research.

#### 1.6.1 Other Publications

The main body of this thesis includes publications to which I made significant contributions. Other publications in which my role was more limited are have been published as follows:

Anatoly Shusterman, Ayush Agarwal, Sioli O'Connell, Daniel Genkin, Yossi Oren, and Yuval Yarom – "Prime+Probe 1, Java-Script 0: Overcoming Browser-based Side-Channel Defenses", USENIX Security 2021.

Zhiyuan Zhang, Mingtian Tao, Sioli O'Connell, Chitchanok Chuengsatiansup, Daniel Genkin, and Yuval Yarom – "BunnyHop: Exploiting the Instruction Prefetcher", USENIX Security 2023.

Bradley Morgan, Gal Horowitz, Sioli O'Connell, Stephan van Schaik, Chitchanok Chuengsatiansup, Daniel Genkin, Olaf Maennel, Paul Montague, Eyal Ronen, and Yuval Yarom –

"Slice+Slice Baby: Generating Last-Level Cache Eviction Sets in the Blink of an Eye", IEEE SP 2025.

# **Chapter 2**

# **Background**

This chapter provides essential background for the rest of the thesis. It is divided into four sections, the first two detail the internal behaviour of processors and techniques that exploit these behaviours to measure internal processor state, while the last two focus on relevant features of web browsers and browser-based attacks.

#### 2.1 Microarchitecture

The *microarchitecture* refers to the internal design of a processor that determines how it executes instructions. It includes components such as caches, buffers, pipelines, execution units, interconnects, and other internal structures. While processors may share the same Instruction Set Architecture (the interface between the hardware and software), their microarchitectures can differ significantly.

Unfortunately, processor vendors rarely publish detailed documentation of microarchitectural behaviour, which has led various research communities to reverse-engineer these details to better understand how microarchitectures operate. The rest of this section provides a concise overview of modern processor microarchitectural behaviours relevant to this thesis.

### 2.1.1 Memory Caches

Modern processors use a cache – small, fast memory located directly on the processor – to reduce the average latency of memory accesses. This improvement is achieved partly

through physical proximity and partly because caches are optimised for low latency at the expense of data density and power efficiency. The processor stores recently accessed data in the cache under the assumption that this data will be reused. When the data is accessed again, the lower latency of the cache results in faster access times, leading to overall performance improvements.

**Structure.** The cache is organised as a *set-associative* structure, consisting of multiple *sets*, each containing multiple *ways*. The processor divides memory into fixed-length units called *cache lines*, which are stored in the cache. Each cache line can only be stored in a single set, determined uniquely by the address of the line, but it can occupy any way within that set. To identify which line is stored in each way, the cache stores the line address (or tag) alongside the data. When the processor performs a memory access, it uses the memory address to determine the set to search, then searches each way for a matching address. If a match is found, the access is a *cache hit*, and the data from that way is returned. If no match is found, the access is a *cache miss*, and the processor instead retrieves the data from system memory or a higher-level cache.

**Hierarchy.** Modern caches are not only set-associative but also organised into a hierarchy. Lower-level caches (closer to the processor cores) typically have lower latency at the expense of a smaller capacity, while higher-level caches have larger capacity at the expense of a higher latency. Usually, the *last-level* cache is shared among all processor cores, whereas the lower-level caches are private to each core.

**Inclusivity.** Some caches are *inclusive*, meaning that lower-level caches contain a strict subset of the data stored in higher-level caches. That is, any data present in an inclusive lower-level cache must also be present in higher-level caches. The processor maintains this inclusive property by ensuring that when data is evicted from a higher-level cache, all-inclusive lower-level caches also evict that data.

Other caches exhibit an *exclusive* property, where lower-level caches do not contain any data that is also stored in higher-level caches. In this configuration, when data is moved from a higher-level cache to an exclusive lower-level cache, the processor preserves exclusivity by evicting the data from the higher-level cache. Consequently, each piece of data exists in only one level of the cache hierarchy at a time.

Caches that are neither inclusive nor exclusive are referred to as *non-inclusive*. Like

2.1. Microarchitecture 17

inclusive caches, data copied to a non-inclusive lower-level cache is retained in the higher-level caches. However, unlike inclusive caches, when data is evicted from the higher-level caches, non-inclusive lower-level caches will continue to retain a copy of the data.

Replacement Policy. Since sets have a fixed number of ways, they can become full. When the processor needs to store a new line in a full set, it makes room in the set by evicting another line and storing that line back in system memory. The line selected for eviction is determined by the cache replacement policy. A commonly used policy is the pseudo-least-recently-used (pLRU) policy, which approximates the behaviour of a true least-recently-used (LRU) policy while requiring fewer resources than a faithful implementation.

#### 2.1.2 Execution

To improve performance, modern processors employ both *out-of-order* execution and *superscalar* execution. Out-of-order execution allows the processor to execute instructions as soon as their dependencies are resolved, rather than strictly following the original program order. Superscalar execution enables each core within the processor to execute multiple instructions in parallel, rather than processing one instruction at a time. Together, these features enhance performance by allowing the processor to hide execution delays and keep its execution units busy with independent instructions.

**Branch Prediction.** Branches limit the effectiveness of superscalar out-of-order execution because the outcome of a branch determines which instructions should be executed next. As a result, all future instructions become implicitly dependent on the branch condition, preventing their execution until the condition is known. Processors remove this implicit dependency by predicting the branch outcome and executing the program under the assumption the prediction is correct. When program execution matches the prediction, the processor saves time since it did not have to wait for the branch condition. In cases where program execution does not match the prediction, the processor is said to have *mispredicted*. To correct the mispredicted branch, the processor '*squashes*' (discards) program execution following the branch, then restarts execution with the correct branch outcome.

#### 2.2 Microarchitectural Attacks

Microarchitectural side-channel attacks exploit the behaviour of the microarchitecture to extract sensitive information from other processes running on the same machine. These attacks leverage unintended links between program secrets and the program's internal behaviour. By observing that behaviour – typically through measurements of contention on shared microarchitectural resources – an attacker can infer those secrets.

In its simplest form, an attack might involve timing how fast a loop executes (Cook et al., 2022). However, often attacks exploit the nuanced behaviour of individual microarchitectural components to induce contention at finer granularities, thereby revealing more detailed information. Research has demonstrated that the behaviour of many microarchitectural components can be exploited to mount side-channel attacks. These components include memory caches Liu et al. (2015); Osvik et al. (2006); Percival (2005); Yan et al. (2019); Yarom and Falkner (2014), branch predictors Evtyushkin et al. (2016); Aciiçmez et al. (2007, 2006); Evtyushkin et al. (2018); Zhang et al. (2020), translation lookaside buffers Gras et al. (2018); Koschel et al. (2020); van Schaik et al. (2018), shared buses Paccagnella et al. (2021); Wan et al. (2022), execution units Aciiçmez and Seifert (2007); Bhattacharyya et al. (2019); Aldaya et al. (2019), or GPUs Wei et al. (2020); Naghibijouybari et al. (2018); Taneja et al. (2023); Cronin et al. (2021); Owens and Wang (2011). The remainder of this section provides background on the techniques used to mount the attacks described in this thesis, along with a brief overview of transient-execution attacks.

### 2.2.1 Cache Timing Attacks

The fundamental idea behind a cache timing attack is that an adversary can infer whether a specific piece of memory is present in the cache by measuring the time it takes to access that memory. Fast access times (typically under a hundred CPU cycles) suggest that the data was served from the cache, meaning the memory was present in the cache at the time of access. Conversely, slower access times suggest that the memory was not cached and had to be fetched from a higher level of the memory hierarchy.

On the surface, revealing whether memory is cached does not appear to expose sensitive information. However, cache state is influenced by memory accesses made by all programs running on the machine and the patterns of those memory accesses are often correlated with sensitive information. By measuring cache state, a cache timing attack can partially reveal these memory access patterns and, in turn, reveal sensitive information.

This thesis mainly employs the Flush+Reload and Prime+Probe techniques to measure memory access patterns. In both techniques, one party accesses memory (the victim), while the other attempts to detect these accesses (the adversary). Although these roles are traditionally referred to as 'victim' and 'adversary' in the literature, this thesis adopts alternative terminology: accessor and observer. This naming scheme is chosen to emphasise the broader applicability of these techniques beyond conventional cross-process attack scenarios. For example, the techniques can be used in reverse engineering, in situations where the accessor and observer are components of the same program, or as building blocks within larger attacks where both roles are performed by the adversary.

**Flush+Reload.** In the Flush+Reload technique (Gullasch et al., 2011; Yarom and Falkner, 2014) the observer starts by flushing the target memory from the cache. The accessor is then allowed to execute, potentially accessing the target memory. After a short interval, typically a few thousand processor cycles, the observer measures the time it takes to access the target memory. Fast access times indicate the memory is stored in the cache, while slower access times suggests absence from the cache.

The primary advantage of Flush+Reload is its ease of use and low noise levels. However, its main limitation is that the accessor and observer must share memory; more precisely, the observer must be able to access the same memory used by the accessor. This requirement significantly restricts Flush+Reload's applicability in adversarial settings simply because the adversary is often unable to access the target memory. Moreover, Flush+Reload depends on specific instructions to evict memory from the cache, further limiting its use to cases where the adversary can execute arbitrary instructions.

**Prime+Probe.** The Prime+Probe technique (Osvik et al., 2006; Liu et al., 2015) overcomes the limitations of Flush+Reload by exploiting contention within cache sets. The observer starts by filling every way of a target cache set with 'junk' data. After the accessor runs, the observer measures the time it takes to access this junk data again. A longer access time indicates that the junk data was likely evicted from the cache, likely because the processor removed it to make room for data accessed by the accessor, causing the access to be served from slower system memory.

The primary advantages of Prime+Probe are that the observer does not need to share

memory with the accessor and does not require special instructions. However, there are two significant challenges to effectively using Prime+Probe.

The first challenge is identifying which junk data to access, known as the (minimal) eviction set. The eviction set consists of enough memory to fill a target cache set – no more, no less. Throughout this thesis, we rely on the excellent method developed by Vila et al. (2019) to find eviction sets.

The second challenge is locating the target cache set to fill, the specific set that serves memory to the accessor. Typically, the observer employs a brute-force approach: building an eviction set for each cache set and then using an attack-specific detection method to determine whether accesses to a given eviction set collide with the accessor's accesses.

Beyond these challenges, Prime+Probe is slower than Flush+Reload because it needs to access an entire eviction set, whereas Flush+Reload only needs to access a single piece of memory. In addition, Prime+Probe yields less precise information than Flush+Reload, as it detects contention caused by any memory access served from the target cache set, not just the specific memory location of interest.

#### 2.2.2 Transient-Execution Attacks

Transient-execution attacks are microarchitectural attacks that exploit the execution of instructions that may later be squashed. In these attacks, the adversary tricks the processor into executing the program incorrectly, causing behaviour that deviates from the original program. This often includes accessing memory the program normally would not be able to access. Although the processor eventually squashes the architectural state associated with this incorrect execution, there is often a delay between incorrectly executing an instruction and squashing its effects. This delay is called the speculation window and it enables an adversary to execute code while the program is in an invalid state. Because the hardware does not revert all microarchitectural state, the adversary can use the speculation window to encode secrets into the microarchitectural state, then later recover those secrets by measuring residual microarchitectural state.

**Inducing Branch Mispredicitons.** This thesis mainly focuses on incorrect program execution caused by branch mispredictions. The technique was first described by Kocher et al. (2019), in which the adversary trains a target branch by repeatedly causing it to be taken. When the processor encounters the same branch in the future, it will predict that

2.3. Browsers 21

the branch will be taken. After this training step, the adversary moves to an attack step where they provide a malicious input. This input would cause the branch to be not taken, but because the processor predicted the branch as taken, it proceeds to take the branch anyway.

Consider, for example, a program that uses a branch to guard an access into an array. Under normal execution, whenever the access is performed the branch verified the provided index was within bounds. However, in a transient-execution attack, this assumption does not hold. The adversary can supply an out-of-bounds index and induce the processor to take the branch. The processor then executes the subsequent instructions, performing an out-of-bounds access reading arbitrary process memory.

Although the processor eventually squashes this incorrect speculative execution, the adversary can still leak the secret through a side channel. Commonly, secrets are leaked through the cache due to well-understood behaviour and numerous established attack techniques.

#### 2.3 Browsers

A web browser is a piece of software that allows users to access and interact with the World Wide Web. Its primary function is to render websites so users can view and engage with their content. Websites consist of various resources identified by a Uniform Resource Locator (URL). To retrieve a resource, the browser connects to a server specified by the URL hostname and port number, then requests the resource using the Hypertext Transfer Protocol (HTTP), referencing the URL path. Some of these resources are webpages, files written in Hypertext Markup Language (HTML) that define the page structure, content, and visual appearance.

# 2.3.1 Same-Site Policy

When two resources interact, the web browser consults a security policy to determine whether the interaction is permitted. Commonly, the browser enforces the same-origin policy, which allows interaction only when the resources share the same origin – defined by the domain name, protocol (such as HTTP or HTTPS), and port number of the server.

Notably, the entire domain is considered. For example, foo.example.com and bar. example.com are different origins because their subdomains, foo and bar, are different.

Websites can opt into different security policies, usually via HTTP Headers – metadata sent along with each resource. One such policy is the same-site policy, which permits interaction between resources served from the same site. Unlike the same-origin policy, the same-site policy considers only the final portion of the domain.

Specifically, the same-site policy considers the Effective Top-Level Domain Plus One (eTLD+1). The Top-Level Domain refers to the final portion of a domain under which websites can be registered (e.g., .com.au or .net). The Effective Top-Level Domain includes domains that allow others to register subdomains (e.g., .github.io or .canva.site). The Effective Top-Level Domain Plus One refers to the domain immediately preceding the effective top-level domain, the part registered by website owners (e.g., example.com or example.github.io).

#### 2.3.2 JavaScript

To enable rich interactive applications, webpages can reference executable resources that browsers download and run on the user's device. These executable resources are typically written in JavaScript – a high-level, dynamically typed, object-oriented programming language featuring prototypal inheritance.

**Objects.** Objects are mutable, user-defined collections of properties. Each property has a name, which must be a string or a symbol, and a value, which can be of any type, including another object. Properties can be added, modified, or removed after the object is created.

Objects inherit behaviour in JavaScript through *prototypal inheritance*. Each object has a special property called its prototype. When a property is accessed on an object but is not found, the JavaScript engine looks for that property on the object prototype instead. Since the prototype may be an object too, the JavaScript engine repeats this process until either the property is found or until there are no more prototypes to check.

**Dynamic Typing and Speculative Optimisations.** In JavaScript, variables do not have fixed types. Instead, any value of any type can be assigned to any variable, even if that variable previously held a value of a different type. JavaScript engines reduce the cost of this dynamic behaviour by employing *speculative optimisations* (Meurer, 2017) which optimise the code under the assumption that variables only store one type of value. This

2.3. Browsers 23

optimisation commonly occurs at the function level, where the engine records argument types each time the function is called. After several calls, the engine uses this recorded type information to generate optimised machine code for the function. However, since future arguments may have different types, the engine inserts checks to verify that the actual argument types match the speculated types. If the types do not match, the engine will discard the optimised code and fall back to a more generic, slower implementation.

**Hidden Classes.** In addition to the challenges of dynamic typing, objects pose their own challenge since properties can be dynamically added or removed. JavaScript engines typically use hashmaps to support this dynamic behaviour, but each property lookup becomes an expensive hashmap lookup. To reduce this overhead, JavaScript engines use *hidden classes* to create a static layout for object properties then cache property lookups as a speculative optimisation (Deutsch and Schiffman, 1984; Chambers et al., 1989; Hölzle et al., 1991).

Hidden classes store properties in two data structures – an array holding the property values and a hashmap mapping properties to their corresponding locations within the array. When a property is added to a hidden class, the engine appends the property value to the end of the array and updates the hashmap to map the property name to the corresponding array location. When looking up a property, whether to read or modify it, the engine uses the hashmap to find the location of the property value in the array. Although this approach still requires a hashmap lookup, the location of the property is shared between all objects with the same hidden class, which enables the engine to cache the lookup as a speculative optimisation.

#### 2.3.3 Browser Architecture

Modern web use often involves visiting multiple webpages simultaneously, each in its own window or tab. Historically, browsers employed a monolithic single-process architecture that handled all browser functions within one process. This architecture is simple, but it suffers from security and stability issues. For example, if a webpage causes the browser to crash, the entire browser crashes affecting unrelated webpages. Likewise, if a malicious webpage exploits a vulnerability in the browser, then the entire browser becomes compromised.

To address this issue, browser vendors adopted a multi-process architecture consisting of several renderer processes and a single compositor process (Reis et al., 2009; Nguyen, 2017). If a webpage causes the browser to crash, only the affected renderer process crashes while the rest of the browser continues unaffected. Similarly, if a malicious webpage exploits a vulnerability, only the affected renderer process becomes compromised.

**Partitions in Chrome.** To reduce the memory footprint of renderer processes, the Chrome browser compresses pointers by representing them as 32-bit offsets from a fixed base address (Sheludko and Solanes, 2020). This base address defines an *isolate* within which memory is allocated. Because pointers are represented as 32-bit offsets, instead of a full 64-bit address, the amount of memory accessible to each pointer is limited. Chrome leverages this limitation as a security feature by carefully arranging the address space so that memory accesses through compressed pointers are constrained to their respective isolate.

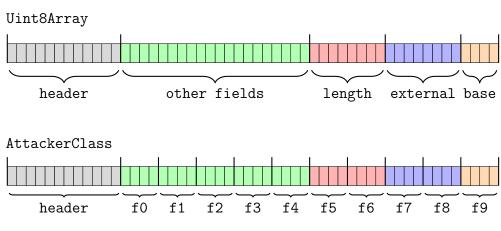

#### 2.3.4 Uint8Array

Typed arrays are a collection of standard objects that enable developers to directly access and manipulate raw binary data using JavaScript. All typed array data is stored within an ArrayBuffer or a SharedArrayBuffer. These buffer objects do not provide an interface for direct data access; instead, one or more typed array views can be instantiated over the buffer to provide an array-like interface. For example, a Uint8Array exposes its underlying buffer as an array of 8-bit unsigned integer values.

Whenever a JavaScript program accesses a typed array, the engine first verifies that the index is valid – specifically, that the index is an integer greater than or equal to zero and less than the array length. If the index is invalid, the engine does not perform any memory access.

**Implementation in Chrome**. In Chrome, typed arrays contain four key fields: the type, a pointer to the underlying buffer, the length of the underlying buffer, and an offset into the underlying buffer (used to implement zero-copy slice operations). To support inexpensive moving and sharing of typed arrays between webpages and JavaScript threads, the underlying buffer is allocated at an arbitrary address outside of any given isolate. Consequently, references to the underlying array buffer are represented as full-sized

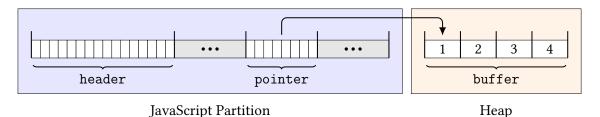

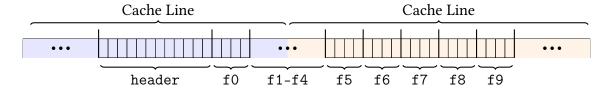

pointers. Figure 2.1 illustrates the memory layout for Uint8Array's implemented in Chrome.

FIGURE 2.1: Uint8Array Memory Layout:

A Uint8Array containing the values 1, 2, 3, 4. Ticks denote the boundaries of fields, rectangles within each field denote a byte, and colours are used to highlight where memory is allocated.

#### 2.4 Browser-Based Attacks

Web browsers are commonly targeted owing to the popularity of the web as a platform and the ease with which an adversary can execute code on a victim's device. Once an adversary tricks a victim into visiting a malicious website, through phishing, malicious advertisements, or other means, they gain the ability to execute code on the victim's device. From there, the adversary can mount a variety of attacks against other open webpages, the browser itself, or the underlying system. Of particular interest to this thesis are microarchitectural attacks launched from the browser (Oren et al., 2015; Shusterman et al., 2019, 2021; Andrysco et al., 2015, 2018). This section provides a brief introduction to website-fingerprinting, history-sniffing, and pixel-stealing attacks.

# 2.4.1 Website-Fingerprinting Attacks

In a website-fingerprinting attack, the adversary attempts to uncover the identity of a website visited by the victim. There are two broad attack models for website-fingerprinting attacks: the on-path and co-located models.

In the more conventional on-path model, the adversary mounts their attack from a separate machine located somewhere along the communication path between the victim and the wider internet (Hintz, 2002; Herrmann et al., 2009; Panchenko et al., 2011; Cai et al., 2012; Gong et al., 2012; Wang and Goldberg, 2013; Juarez et al., 2014; Hayes and Danezis, 2016; Panchenko et al., 2016; Rimmer et al., 2018; Jansen et al., 2018; Li et al., 2018). This position enables the adversary to monitor network packets sent to and from the victim. Since the contents of each packet are assumed to be encrypted, the adversary is limited to only using packet size and the timing between packets to fingerprint a website. Consequently, countermeasures against on-path attacks typically focus on injecting random delays or spurious traffic to mask these patterns.

Under the co-located model, the adversary mounts their attack directly from the victim device. This position enables the adversary to indirectly monitor the browser behaviour through side channels including microarchitectural side channels (Oren et al., 2015; Shusterman et al., 2021, 2019; Cronin et al., 2021; Naghibijouybari et al., 2018; Taneja et al., 2023; Cronin et al., 2021).

In either model, the adversary samples browser behaviour over time to construct a fingerprint then matches it with previously recorded fingerprints to identify the website.

#### 2.4.2 History Sniffing Attacks

In a history-sniffing attack, the adversary aims to reveal the victim's browsing history. The defining characteristic of this attack is that the adversary cannot directly access the history itself. Instead, they rely on an oracle that reveals whether a given URL exists in the victim's browsing history then they query the oracle with a large number of URLs to partially reconstruct the victim's browsing history.

Many history-sniffing attacks exploit the :visited CSS selector, a usability feature in browsers that allows pages to change the style of visited links. Using this method, the adversary creates a page containing multiple links with URLs they wish to query. The adversary then checks which links have been styled to reveal which URLs have been visited by the victim. Early attacks could directly read which styles were applied to a link or could use styles that would alter the page layout to indirectly reveal whether the style had been applied (Smith et al., 2018; Janc and Olejnik, 2010). In response, browser vendors deployed countermeasures that remove differences between visited and unvisited

link styles. Specifically, whenever a website attempts to query the browser, the browser will always behave as though the URL is unvisited. In cases where the style makes this impossible, the browser will simply refuse to apply the style at all.

More recent history-sniffing attacks have bypassed these countermeasures by exploiting timing side channels. Specifically, the adversary creates a style that is computationally expensive for the browser to apply and uses the :visited selector to apply this style. By monitoring for performance degradation, the adversary can infer whether the style was applied (Smith et al., 2018). In response, browser vendors further restricted allowed styles to a limited set believed to have low performance overhead, such as changing the text colour or background colour of links (MDN Contributors, b).

#### 2.4.3 Pixel-Stealing Attacks

Pixel-stealing attacks are timing attacks that induce data-dependent delays in browser rendering to reveal sensitive information displayed on the screen. These attacks apply a malicious style, designed to be expensive to compute for certain colours but cheap for others, to an HTML element to create a delay dependent on the element colour. If the difference in computation time is large enough, the browser misses the deadline to render the next frame, an event that an attack can detect to reveal the original element colour.

**SVG Filters.** Attacks typically use SVG filters to create computationally expensive styles. These filters are small user-defined functions (originally specified by the SVG standard) that are intended to enable artistic effects, such as blurring, which are difficult or impossible to achieve with standard HTML and CSS alone. Filters are composed of several filter elements, primitive operations that the webpage provides parameters for, that are combined together to form a complete filter. The list of filter elements is specified by the SVG standard and includes several standard image filtering operations such as colour mapping and convolutions.

Listing 2.1 demonstrates how to apply a filter to a div element. Lines 3-8 define an SVG object. Inside the object, Lines 4-7 define the filter. This filter consists of two elements executed sequentially: A Gaussian blur (Line 5) and image dilation (Line 6). Finally, Line 11 applies the filter to the target div element.

**Stealing Cross-Origin Content.** Filters can be applied to cross-origin content to allow designers to create webpages with cohesive filtered appearances. This is assumed to

```

<html>

<head>

<svg><defs>

<filter id="filter_id">

<feGaussianBlur stdDeviation="1" />

<feMorphology operator="dilate" radius="2" />

</filter>

</defs></svg>

</head>

<body>

10

<div style="filter: url(#filter_id)"><!-- content --></div>

11

</body>

12

</html>

13

```

LISTING 2.1: **SVG Filter Example:** A demonstration of how to define an SVG filter and apply it to a specific element on a webpage.

be safe because the browser restricts access to the output of the filter. Unfortunately, the presence of side-channels invalidates this assumption and enables adversaries to recover cross-origin content. Previous studies has demonstrated how differences caused by algorithmic optimisations in SVG filters (Stone, 2013; Kotcher et al., 2013), computations on subnormal floating-point numbers (Andrysco et al., 2015; Kohlbrenner and Shacham, 2017), and frequency scaling in modern CPUs and GPUs (Wang et al., 2023; Taneja et al., 2023) can be exploited to mount pixel-stealing attacks.

# **Chapter 3**

# **Attributing Microarchitectural Leakage within Systems**

Several approaches exist for analysing microarchitectural side-channel leakage, with the most common method being to reverse-engineer a model of the behaviour of a specific hardware component and then develop an attack that exploits that behaviour. The successful execution of the attack is taken as evidence that the reverse engineering is accurate, and the resulting model is used to provide insight into the leakage. Many studies have employed this approach for various components, including memory caches (Liu et al., 2015; Osvik et al., 2006; Percival, 2005; Yan et al., 2019; Yarom and Falkner, 2014), branch predictors (Evtyushkin et al., 2016; Actiçmez et al., 2007, 2006; Evtyushkin et al., 2018; Zhang et al., 2020), translation lookaside buffers (Gras et al., 2018; Koschel et al., 2020; van Schaik et al., 2018), shared buses (Paccagnella et al., 2021; Wan et al., 2022), execution units (Actiçmez and Seifert, 2007; Bhattacharyya et al., 2019; Aldaya et al., 2019), and GPUs (Wei et al., 2020; Naghibijouybari et al., 2018; Taneja et al., 2023; Cronin et al., 2021; Owens and Wang, 2011).

This approach works well when analysing information leakage from specific components; however, it is less suited to analysing coarse-grained leakage. Such leakage occurs in attacks that monitor the system over extended periods of time or monitor large portions of the microarchitectural state. In either case, it can be difficult to attribute leakage to any singular microarchitectural effect. The challenge is further compounded by the use of machine learning classifiers to extract information, as it further obscures which factors contributed to a successful attack.

As an example of this challenge, consider the cache-occupancy website-fingerprinting

attack. In this attack, the adversary measures the speed at which they can repeatedly iterate though a large buffer of memory to infer which website a victim visits. Successful cache-occupancy attacks demonstrate that information must be leaked, but Shusterman et al. (2019) and Cook et al. (2022) provide competing explanations for the mechanism behind this leakage.

Shusterman et al. (2019) propose that browser memory activity causes evictions in the adversary's buffer which, in turn, affects the adversary's iteration frequency. Cook et al. (2022) question this explanation and argue that operating system interrupts better correlate with the adversary's iteration frequency.

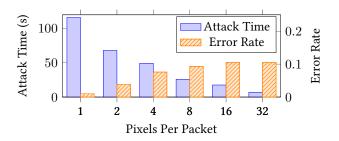

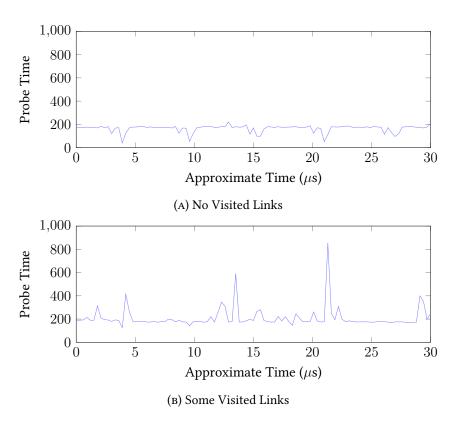

Several studies have begun to tackle this problem. Gülmezoglu (2021) proposed an approach that uses explainable AI techniques to reveal which browser behaviours leak the most information. Specifically, they annotate browser behaviour and record it alongside HPCs. Then, they train a machine learning model to distinguish websites based on the HPCs and use explainable AI to identify which measurements – and by extension, which browser behaviours – provided the most information to the model. While this approach effectively highlights which browser behaviours leak information to an adversary, it falls short of explaining how the leaked information propagates through the microarchitecture to the attacker, insight that is crucial for designing effective countermeasures.